### 1. Das Projekt "Die Leiterplatte 2010"

#### Die Idee

Die "LP2010" steht als Synonym für die Applikationsplattform "Meltemi" der Fa. Unit^el aus Graz.

In der ELEKTRONIKPRAXIS wurden 14

Kapitel über die gesamte Entwicklung und dieser Baugruppe vom Levelle zum EMV-Test veröffent.

Die Autoren haben Entscheidungshilfen gegeben und Alternativen beschrieben, die bei einer so komplexen Herausforderung eine erfolgversprechende Lösung für eine stabile Board-Hardware darstellen. Es ist die **Idee** entstanden, die "LP2010" als praxisbezogenes Gemeinschaftsprojekt über einen längeren Zeitraum mit mehreren Partnern weiterzuführen.

# 1.1 Das Baugruppenkonzept

#### Die "Leiterplatte 2010"

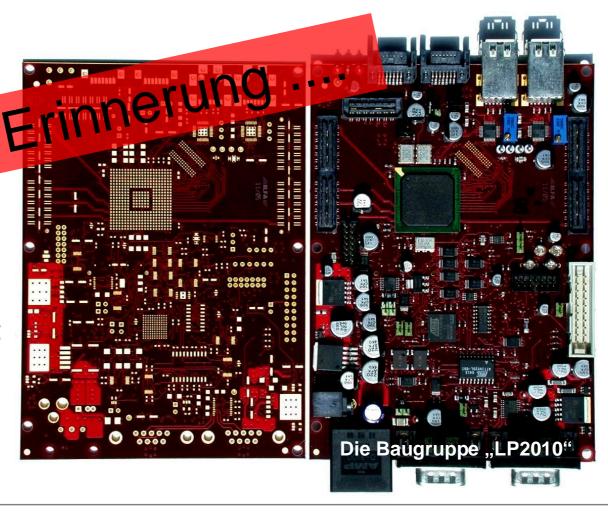

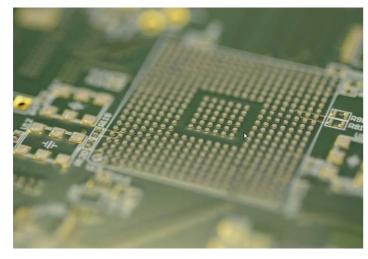

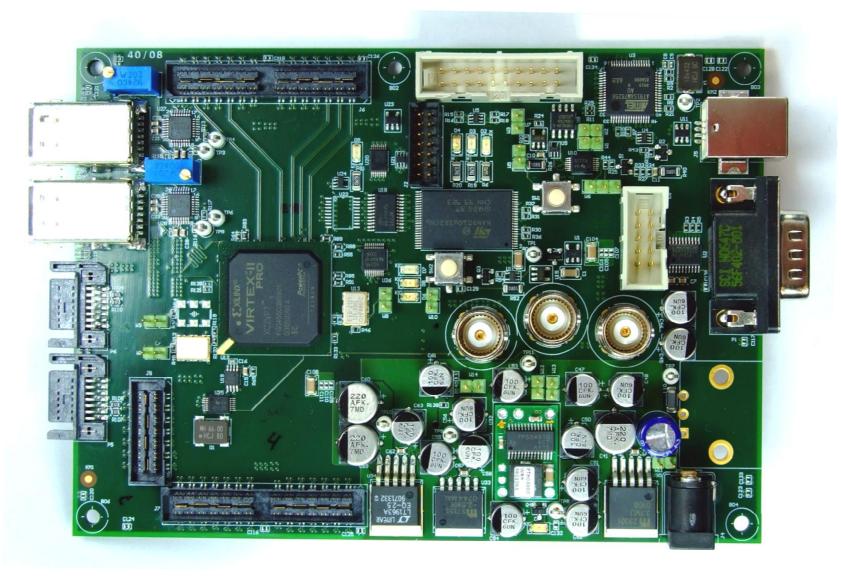

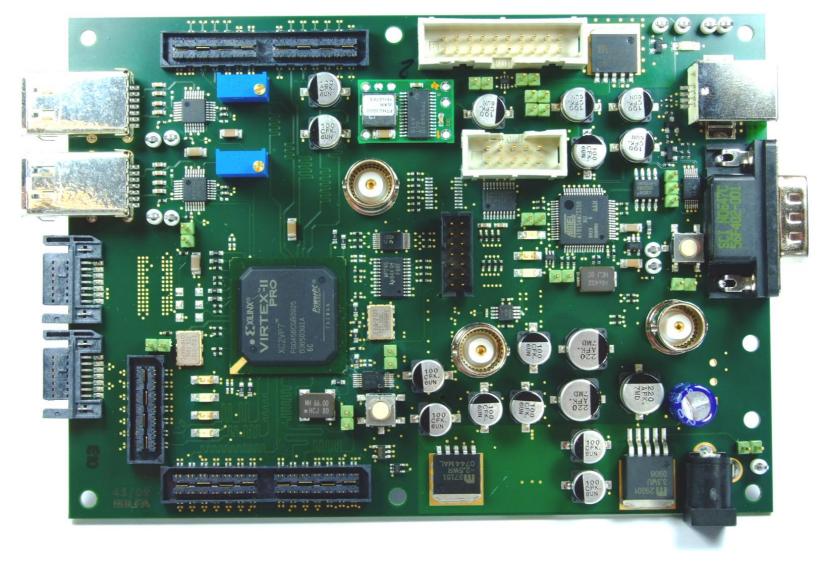

Die "LP2010" basiert auf er High-Speed-CPU "meltemi" der Fa. Unit^el, einer Entwicklung von Herrn Gerhard Eigelsreiter.

### Eigenschaften

- Datatransfer > 4 GBit/s Zur

- EMV-Stabilität

- Signalintegrität

- Impedanzdefiniert

- MPS

- C-Gruppen

### 2. Ergebnisse

#### Wie ist es ausgegangen?

Die Projektpartner DesContec (jetzt FlowCAD), TAUBE und ILFA haben Anfang 2008 jeweils ein eigenes CAD-Layout fertiggestellt.

ILFA hat zu diesen Layouts im Herbst 2008 die Leiterplatten gefertigt.

Im Frühjahr 2009 hat Frau Mallok die Bauteil-Logistik aufgebaut.

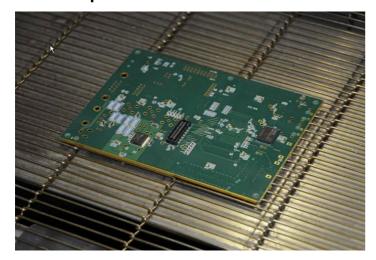

Im August 2009 hat die Fa. Taube diese Leiterplatten bestückt.

Die fertigen Baugruppen wurden Anfang September 2009 von Herrn Eigelsreiter in Betrieb genommen.

Mitte September 2009 wurden die Baugruppen in Wien im EMV-Labor des TGM von ihm in einem ersten Abschnitt getestet.

Alle getesteten Baugruppen haben die Anforderungen bestanden.

# 2.1 Ergebnisse

#### Gab es Komplikationen?

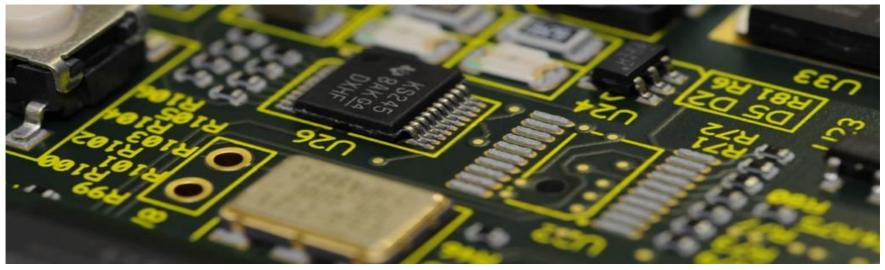

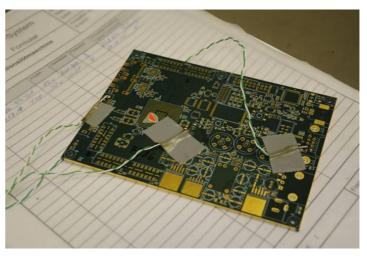

Auszüge aus den Protokollen der Fa. Taube (August 2009) :

..... Kameramarken fehlen / R53 falsche Bauform, Soll 1206 Ist 0402 / R137 falsche Bauform Soll 0603 Ist 0402 / C41,59,60 falsche Bauform Soll Alu-SMD Case E Ist Case D / Für U24 falscher Werteintrag und falsches Bauteil im Design, Korrektur erfolgt durch Montage eines Vergleichstyps, äußere Anschlüße aufbiegen, Handlöten / U11 ohne Pin-1-Kennung / LEDs ohne Polaritätskennzeichnung, Zuordnung auch im Bestückungsplan nicht ausgewiesen / U18 falsches Bauteil Soll Raster 0.65mm Ist 0.4mm, Ersatztyp beschaffen und Umlöten......

Information von Herrn Eigelsreiter (Mitte September 2009):

2 Baugruppen lassen sich nicht in Betrieb nehmen und werden vorerst wegen Zeitmangel zurückgestellt.

Also: Alles ist ganz normal gelaufen.

| TAURE E              | LECTRONIC GmbH        |

|----------------------|-----------------------|

| 1100 -               |                       |

|                      |                       |

| Circle               |                       |

| 14 mm - 000 Territ   | L. 1987 - 4-18        |

| freeza i an Amerikan | 2° 1° 3002° a ja      |

| ATT THE PARTY        | 27 E 27 E 1 A 1 A 2 E |

| WHAT IS THE          | -9190                 |

| + 111X               | 2144                  |

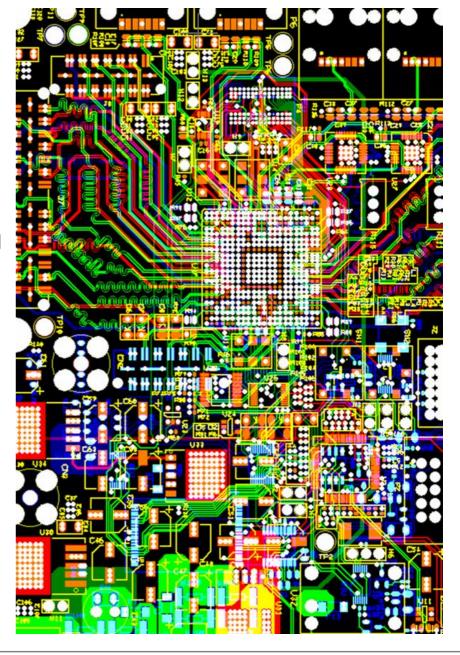

# 3. CAD-Layout-Erstellung

#### ...das erste Layout

Ist es möglich, mit einem komplett neu einzurichtenden CAD-System ein Layout mit 16-Lagen, Dutzenden von LVDS-Verbindungen, Microvias, Pluggen und Kantenmetallisierung zu erstellen, das dann auch funktioniert und zu einer Baugruppe führt, die im EMV-Labor alle Anforderungen auf Anhieb besteht?

Es ist möglich.

Das spricht für das CAD-System.

Und für die Layouterin.

### 4. Schaltplan

#### Dokumentation der Schaltpläne für die "LP2010"

Es ist bewußt Teil des Projektes, die Schaltpläne offenzulegen.

Damit soll die Möglichkeit gegeben werden, eine in der Öffentlichkeit intensiv dokumentierte Baugruppe von der Funktion her nachvollziehen und gegebenenfalls auch weiterentwickeln zu können.

Die Interpretation der Schaltpläne gestattet einen Blick hinter die Kulissen eines Schaltungskonzeptes, das eine Lösung für eine High-Speed-CPU auf hohem Niveau bietet.

Die fachlich orientierte Diskussion rund um die "Leiterplatte 2010" führt zu einem beträchtlichen Zugewinn an Kompetenz. Für Schulen, für Universitäten und selbst für professionelle Entwickler im Beruf ist die LP2010 eine Referenzprodukt, an dem Alle lernen können, die sich mit den Anforderungen anspruchsvoller Elektronik auseinandersetzen wollen - und müssen.

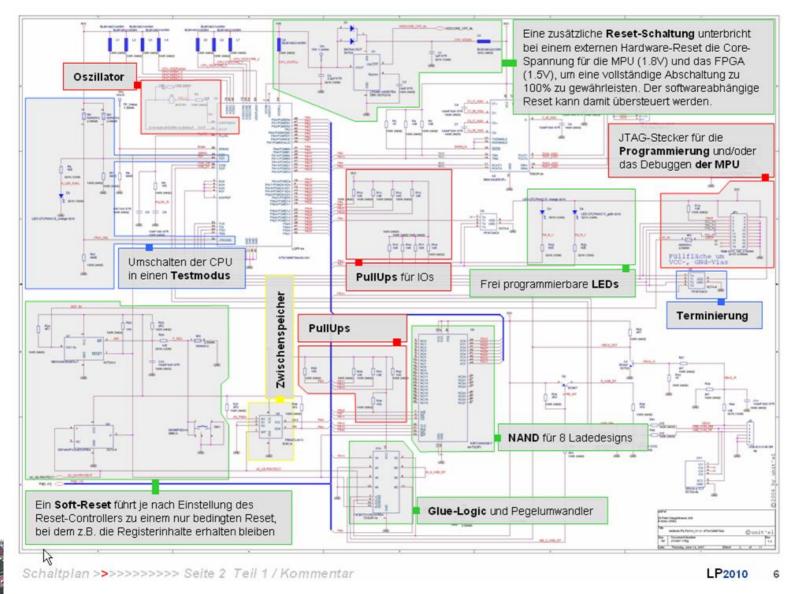

### 4.1 Schaltplan

### Reset, PullUps, Glue-Logic, NAND und Terminierung (Auszug)

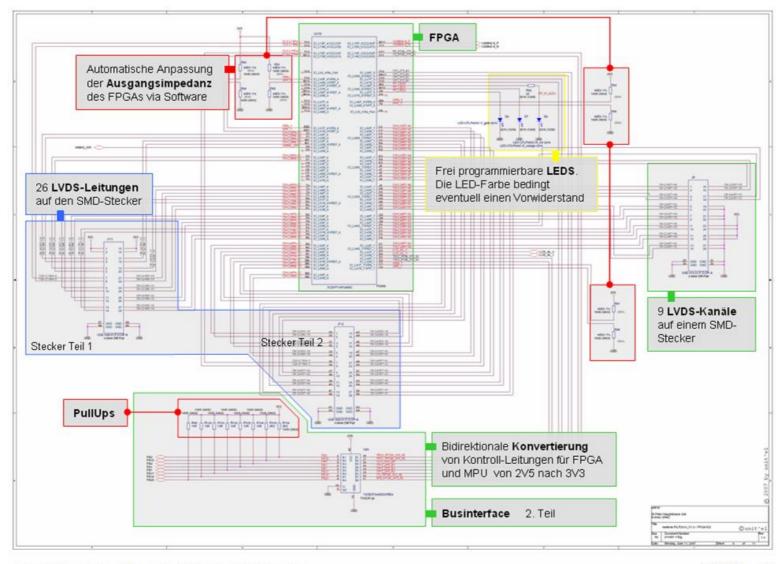

### 4.2 Schaltplan

#### FPGA, Businterface und LVDS-Leitungen (Auszug)

Schaltplan >>>>>>> Seite 6 / Kommentar

LP2010

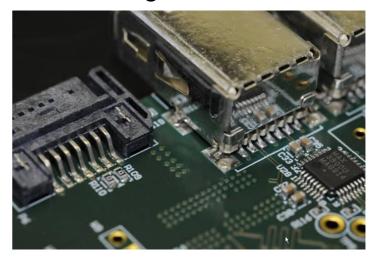

# 5. Baugruppenproduktion

#### Bestückung von Leiterplatten

Zu den Teilaufgaben des Projektes gehört auch die Dokumentation der verschiedenen Fertigungsabläufe in den Disziplinen CAD, Leiterplattenfertigung und Baugruppenproduktion.

Baugruppen auf dem Level von High-Speed-Anwendungen sind ohne Kenntnis des vollständigen Weges, den das Produkt durchlaufen muß, und den Einflüssen, denen es dabei unterliegt, nicht mehr erfolgreich umsetzbar.

Die Ausbildung aller Menschen, die in diesen Bereichen arbeiten, muß deshalb komplett und fachlich fundiert sein.

Foto Rainer Taube

### 5.1 Baugruppenproduktion

#### **Impressionen 1**

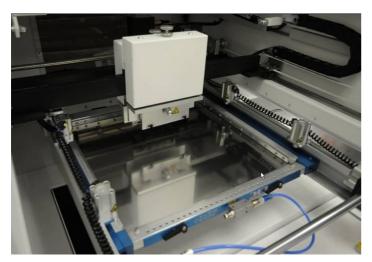

Lotpastendruck mit Metallschablone

Lotpastendruck für das BGA

Einrichten des B.-Automaten

Bestückung im Automaten

-otos Rainer Taube

### 5.2 Baugruppenproduktion

### **Impressionen 2**

Transportbox

Einfahrzone zum Reflowautomaten

Profilierung für Reflow

Kontrolle des Lötergebnisses

-otos Rainer Taube

# 6. Kantenmetallisierung

#### **Baugruppe Nr. 1 / Variante ilf8i160**

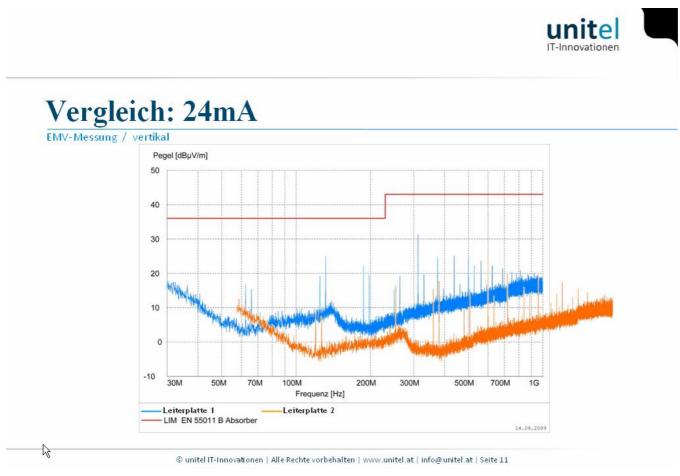

Die Aufgabe der Kantenmetallisierung ist, die Baugruppe mit Blick auf die EMV-Stabilität abzuschirmen.

Störungen von außen sollen im Idealfall völlig ohne Einfluß auf die Funktion der Baugruppe bleiben.

Andererseits soll die Baugruppe nicht selbst Einfluß auf die Funktion benachbarter Baugruppen haben.

Die Meßergebnisse im EMV-Labor bestätigen diesen Effekt tendenziell bereits unter Teil-Last der in Betrieb genommenen Baugruppe.

### 7. Baugruppen

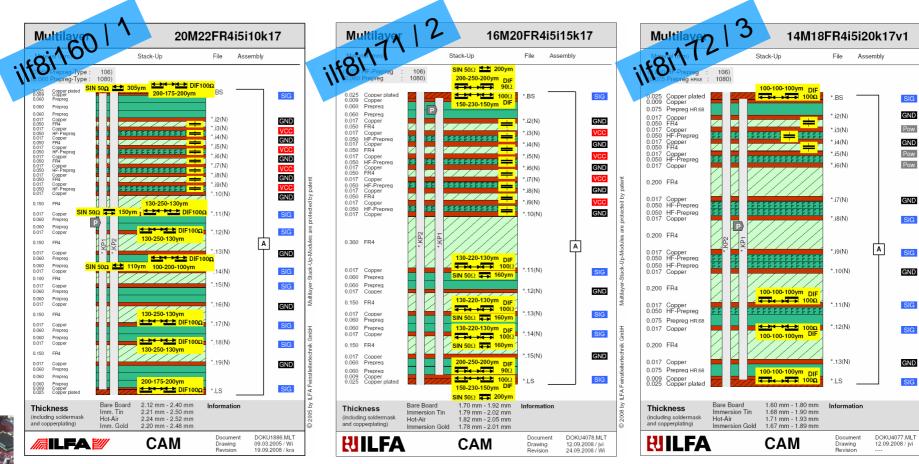

### Die Multilayer-Baupläne

Die Multilayer-Baupläne sind für alle CAD-Layouts unterschiedlich. Die Anzahl der Signal- und der Stromversorgungsebenen variiert. Diese Variationen liegen im Ermessen des Designers/der Designerin.

# 7.1 Baugruppe Nr. 1

#### Variante ilf8i160

# 7.2 Baugruppe Nr. 2

#### Variante ilf8i171

# 7.3 Baugruppe Nr. 3

### Variante ilf8i172

#### 8. EMV-Labor

#### Die Meßergebnisse....

..... finden sich in dem Vortrag von Herr Eigelsreiter.....

Vielen Dank an Alle, die mitgeholfen haben, dieses Projekt möglich zu machen.