# B 19126 April 2007 € 9.20

# Kompendium für Hardware-Entwickler Schnelle differenzielle Signale entflechten Die Vorteile der Kantenmetallisierung Multilayer-Systeme konstruieren Seite 20 Kriterien für den optimalen Lagenaufbau

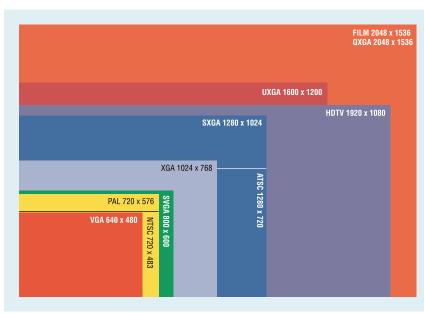

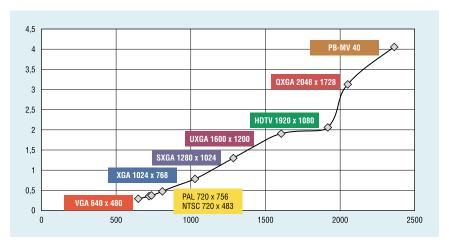

55 HDTV-Bilder in Echtzeit verarbeiten

Seite 47 Powerplane-Systeme EMV-günstig auslegen

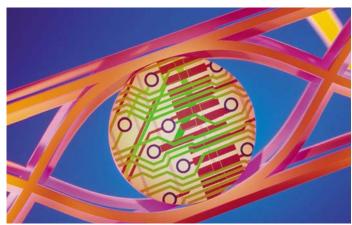

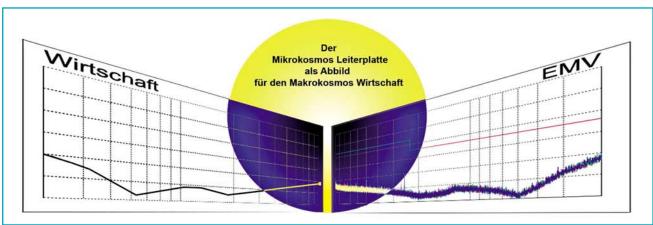

## Die Leiterplatte 2010

Claudia Mallok

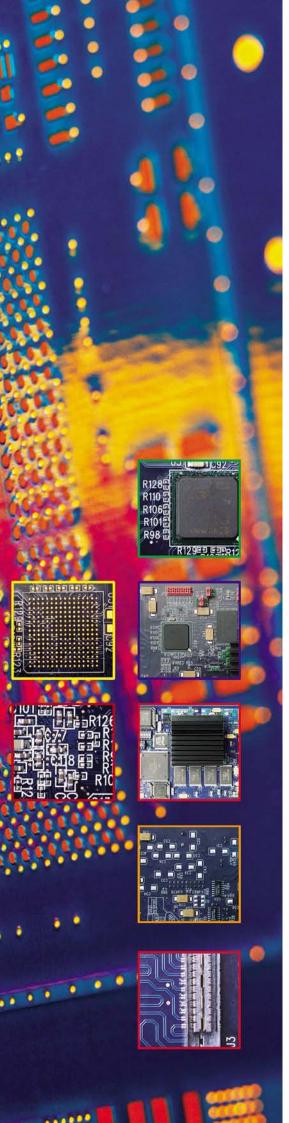

"Die Leiterplatte 2010" ist die Fortsetzung der erfolgreichen Beitragsreihe "Die Leiterplatte 2005", die im Jahr 2003/2004 einen Standard gesetzt hat. Wieder steht "Die Leiterplatte 2010" für einen ganzheitlichen Ansatz Elektronik zu betrachten und zu realisieren. Von der Auswahl der Bauelemente, über

das EMV-gerechte und physikalisch richtige Design bis zur Produzierbarkeit der Leiterplatte und Bestückung der Baugruppe.

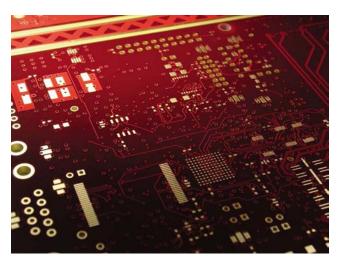

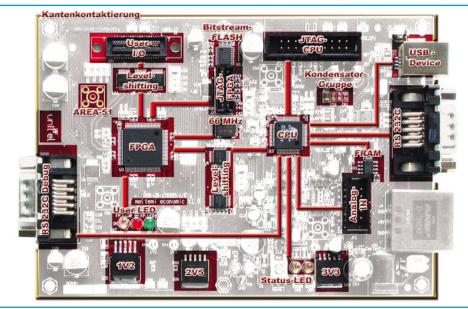

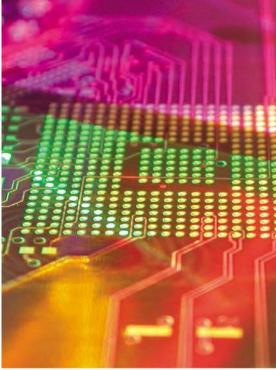

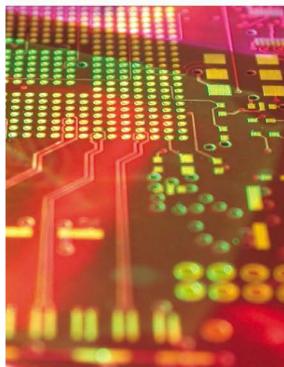

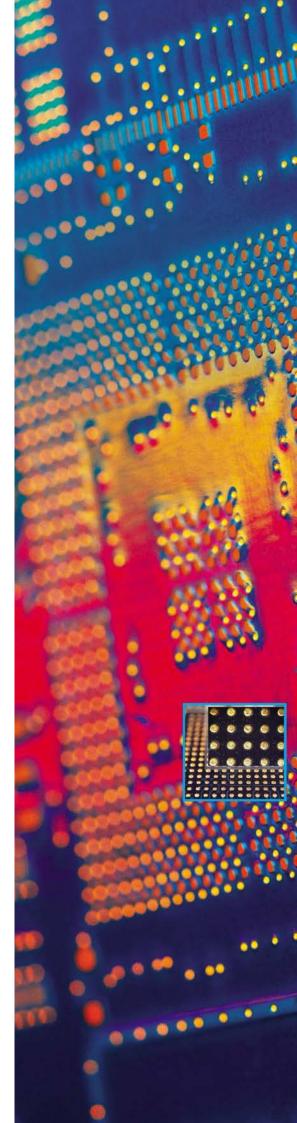

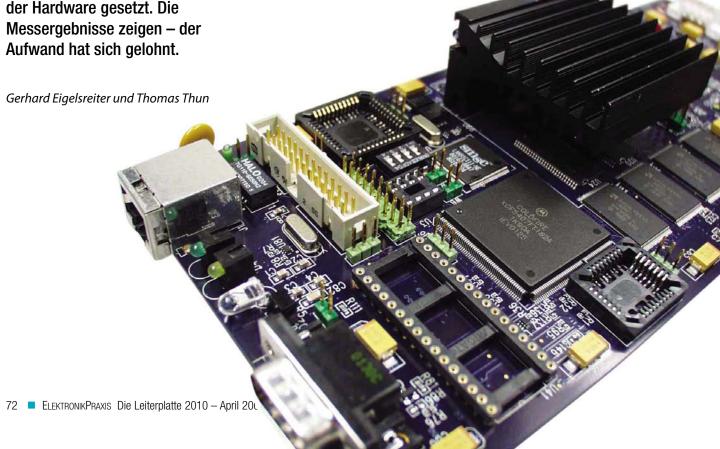

Im Mittelpunkt steht diesmal die Baugruppe meltemi, eine Applikationsplattform ausgelegt für Übertragungsbandbreiten von bis zu 60 GBit/s in HDTV-Anwendungen, Bildverarbeitung

Experten zeigen ein Referenzdesign für stabile High-Speed-Baugruppen oder sehr schnellen Datenmultiplexern. Ihre Merkmale sind die intensive Berücksichtigung der Signalintegrität, der schnelle Datentransfer via LVDS, eine extreme EMV-Spezifikation und die kapazi-

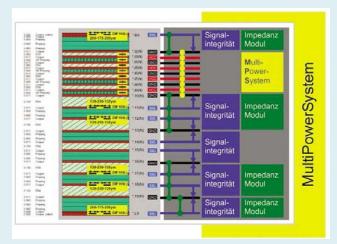

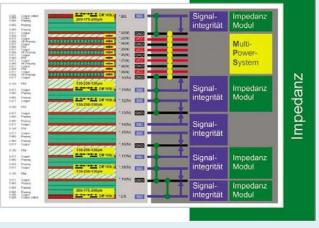

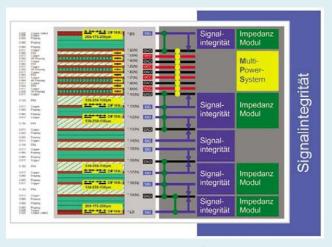

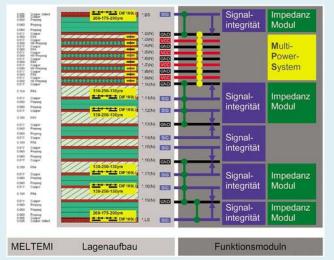

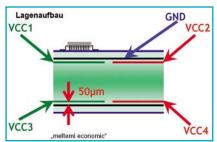

tive Nutzung von Powerplanes. Die Leiterplatte zu meltemi ist ein 20-lagiger Multilayer mit einem Multi-Power-System in 50-µm-Abständen, gepluggten Vias und Kantenkontaktierung.

In 14 Kapiteln zeigen die beteiligten Partner die Entwicklung der meltemi-Baugruppe von der Bausteinauswahl bis zum EMV-Test im Messlabor auf. Die Experten geben Entscheidungshilfen und beschreiben Alternativen, die bei einer so komplexen Herausforderung eine Erfolg versprechende Lösung für eine stabile Board-Hardware darstellen. Und weil die Autoren oft auf die Beiträge der Vorgängerserie verweisen, liefern wir die Beiträge als Grundlagen gleich mit. Diese finden Sie ab Seite 62 bis 79.

Das meltemi-Projekt verdeutlicht, dass die Konstruktion einer komplexen Baugruppe eine große Herausforderung für jeden Entwickler darstellt, der die Fortschritte der Bauteiltechnologie, die Möglichkeiten der Leiterplattenproduktion und Layoutgestaltung am CAD-System zusammenführen muss. Das Projekt zeigt auch, dass nur die gemeinsame, partnerschaftliche Herangehensweise an ein progressives Projekt, also die Berücksichtigung aller Anforderungen der eingebundenen Fachbereiche, zu einer ganzheitlich funktional optimierten Baugruppe führt.

claudia\_mallok@elektronikpraxis.de

ERSA GmbH, 97877 Wertheim/Germany Tel. +49(0)9342/800-0 · e-mail: info@ersa.de

## PATI 2007 ELEKTRONIK April 2007

#### Serielle Hochgeschwindigkeits-Datenübertragung

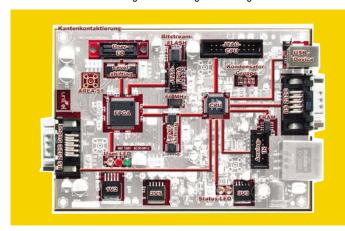

"meltemi" steht für eine CPU-Plattform für die serielle Hochgeschwindigkeitsdatenübertragung im Multi-Gigabit/s-Bereich – hochintegrierte Transceivertechnik macht's möglich. Den Einfluss der seriellen Transceiver auf die Störabstrahlung und Stabilität der Baugruppe beschreibt Kapitel 1. **Seite 6**

Eine Besonderheit der meltemi-Leiterplatte ist die Kantenkontaktierung, die sich messbar vorteilhaft im Hinblick auf EMV, Signalintegrität und Entwärmung bei vergleichsweise vernachlässigen Kosten auswirkt. Die dritte Dimension der Leiterplatte steht im Mittelpunkt von Kapitel 3. **Seite 16**

#### EMV-günstige Powerplane-Systeme designen

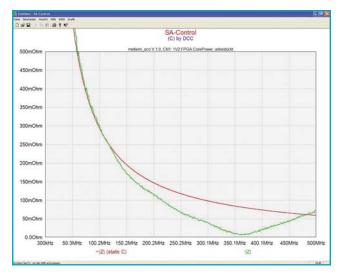

Beim Design von flächigen Stromversorgungssystemen so genannten Powerplanes kämpft der Entwickler gleich an mehreren Fronten gleichzeitig. Eine leistungsfähige Stützung zu gewährleisten und eine effiziente Entkopplung sind zwei der wichtigsten Aufgaben. **Seite 47**

#### **Zweidimensionale Bildverarbeitung mit FPGAs**

Aufgrund ihres Aufbaus sind FPGAs für zweidimensionale Bildverarbeitungsaufgaben prädestiniert. Im Zusammenspiel mit einem geeigneten Controller bzw. Prozessor lässt sich gerade bei der Echtzeit-Bildverarbeitung und großen Bildformaten die Rechenzeit signifikant beschleunigen. **Seite 59**

- 6 Serielle Hochgeschwindigkeits-Datenübertragung Die Auswirkungen der seriellen Transceiver

- **12 Schnelle differenzielle Signale entflechten** Die High-Speed-Regeln beachten

- 16 Die physikalischen Eigenschaften revolutioniert Metallisierung der Leiterplattenkanten

- 20 Was moderne Multilayer-Systeme leisten können Ein elegantes Chaos

- 24 Die Konsequenzen für Entflechten und Routing Nur ein Stück Draht

- 28 Signalqualität der Datenübertragungsleitungen analysieren In der EMV-Prüfhalle I

- 32 Einfluss von FPGAs auf das Abstrahlverhalten der Baugruppe In der EMV-Prüfhalle II

- **36 Die Quadratur des Kreises I** Stabile Hardware im 6-Lagen-Aufbau

- 39 Die Quadratur des Kreises II Stabile Hardware im schlanken 6-Lagen-Aufbau

- **42 Der optimale Lagenaufbau für das Multilayer-System** Philosophische Spannungen I

- **45 Der optimale Lagenaufbau für das Multilayer-System** Philosophische Spannungen II

- 47 EMV-günstige Powerplane-Systeme designen Der Kantenkondensator

#### InfoClick ist der Online-Service für ELEKTRONIKPRAXIS-Leser!

Und so funktioniert's: Sie geben den sechsstelligen Code, den Sie unter jedem Beitrag im Magazin finden, ins InfoClick-Feld auf unserer Homepage www.elektronikpraxis.de ein. Sofort haben Sie neben dem direkten Link zur Lieferquelle oder dem Autor des Beitrages Zugriff auf viele weitere nützliche Informationen wie Datenblätter, kostenlose Downloads, Veranstaltungen u.v.m.

#### Die Quadratur des Kreises

Die Entwickler haben sich das Ziel gesteckt, ihre Erfahrungen von 18- und 20-lagen Multilayern annähernd verlustfrei in ein 6-Lagen-Multilayer-Design mit einseitiger Bestückung zu komprimieren. Aus dieser Vorgehensweise lassen sich Konstruktionsregeln für künftige Schaltungen ableiten. **Seite 36**

#### EMV-günstige Verhältnisse auf einer Mikroprozessorkarte

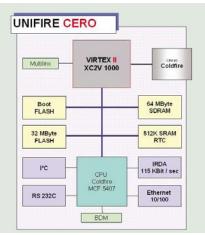

EMV und Gerätefunktion sind so stark miteinander verflochten, dass sich ohne gute EMV die stabile Gerätefunktion nicht gewährleisten lässt. Am Beispiel des CPU-Moduls CERO, dem Vorgänger von meltemi, erklärt EMV-Experte Prof. Christian Dirks die Zusammenhänge und Lösungen. Seite 76

- 51 Die Auswirkungen von Powerplanes Quite please!

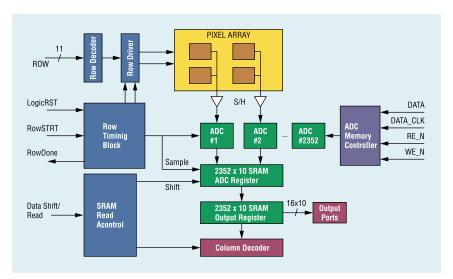

- 55 Applikationsbeispiel Echtzeitbildverarbeitung Bewegtbilder mit hoher Ortsauflösung

- 59 Applikationsbeispiel Echtzeitbildverarbeitung Zweidimensionale Signalverarbeitung mit FPGAs

- 62 Die Leiterplatte 2005 Grundlagen I bis IV Die Beitragsreihe über das CPU-Modul CERO

- 3 Editorial

- 83 InfoClick-Service mit Zusatzinformationen

- 83 Inserentenverzeichnis

- 83 High-Speed-Seminare des FED

- 84 Impressum

## Neue Hochstromkonzepte mit Leiterplatten, Entwärmungskonzepte

FPC & Mechatronik Smart-Flex 3D-Geräte-und Bedienungskonzepte

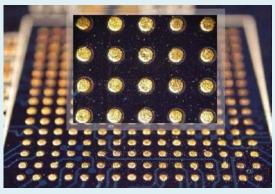

Miniaturisierung µBGA, FC, COB, High speed-Signalübertragung

Design, Entwicklung & Beratung

Manufacturing Services für

Muster und Serien in allen Stückzahlen

## HIGH DENSITY HIGH SPEED · HIGH POWER

GESELLSCHAFT FÜR ELEKTRONIK U. DESIGN MODERNE VERBINDUNGSTECHNOLOGIEN

www.GED-PCB-MCM.de phone o 22 47 / 92 19 -0

Serielle Hochgeschwindigkeits-Datenübertragung

## Die Auswirkungen der Transceiver

Hochintegrierte Transceiver-Technik macht's möglich: serielle Datenübertragungsraten statt bisher 400 MBit/s respektive 600 MBit/s pro LVDS-Kanal von 2,5 GBit/s pro CML-Kanal (5 GBit/s Full-Duplex). Wer in Zukunft mit moderaten Übertragungsraten auszukommen glaubt, kommt trotzdem nicht umhin sich mit High-Speed-Technologien zu beschäftigen. Grund sind die Flankensteilheit der Signale und Störeinträge durch die Stromversorgungs-Pins der Chips. Kapitel 1 zeigt die Auswirkungen der seriellen Transceiver hinsichtlich Störabstrahlung und Stabilität der Baugruppe.

Gerhard Eigelsreiter

Als "Etesien" (leitet sich von 'etos' – jährlich her) bereits den alten Griechen geläufig, ist der Meltemi ein Schönwetterwind, der aus nördlichen Richtungen weht und im Sommer als angenehm kühlend empfunden wird. Sein Ursprung liegt in der nördlichen Ägäis. Stets heiteres Wetter und gute, klare Sicht sind seine herausragenden Merkmale.

Klare und gute Sicht ist auch für jeden dringend notwendig, der sich den höheren Gefilden der seriellen Hochgeschwindigkeits-Datenübertragung mit Transferraten im Multi-Gigabit/s-Bereich hardwareseitig widmen möchte. Um diese gute Sicht nicht aus den Augen zu verlieren stand der Name "meltemi" Pate für das Hardwareprojekt "Die Leiterplatte 2010".

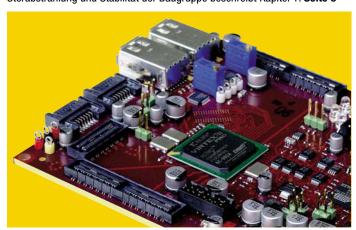

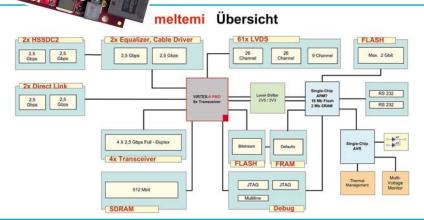

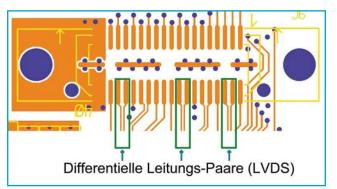

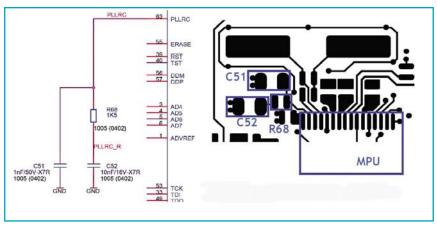

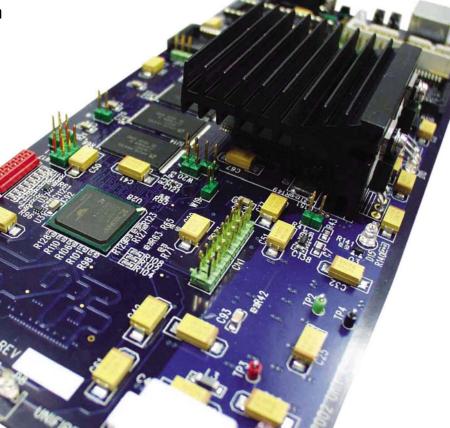

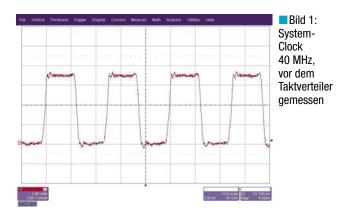

Ziel der Beitragsreihe ist es ein wenig Licht in das Rundherum einer solchen Entwicklung zu bringen, Entscheidungshilfen zu geben und Alternativen zu beschreiben, die bei einer derart komplexen Herausforderung einen Erfolg versprechenden Weg aus einem Labyrinth an Lösungswahrscheinlichkeiten zu einer stabilen Board-Hardware weisen. Zentraler Dreh- und Angelpunkt des meltemi-Board ist ein FPGA mit integrierten seriellen Transceivern, umgeben von fest verdrahteter Unterstützungslogik und einem 32-Bit-Single-Chip-Mikrocontroller (Bild 1). Die mittels FPGA nach außen geführten Eingangs/Ausgangs-Ports sind samt und sonders in differenzieller Leitungstechnik ausgeführt. Von den insgesamt 77 differenziellen Kanälen sind 61 in LVDS-Technik mit einer Übertragungsrate von 600 MBit/s/Kanal, also insgesamt mehr als 36 GBit/s brutto ausgestattet. Die restlichen 16 Kanäle werden von acht integrierten Transceivern mit 2,5 GBit/s/Kanal, insgesamt 40 GBit/s brutto, abgedeckt

## 77 differenzielle Kanäle und 61 LVDS-Leitungspaare

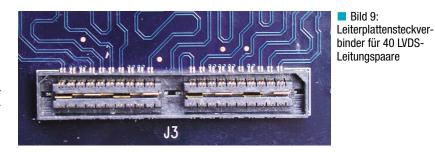

Vier Transceiver-Verbindungen laufen über jeweils zwei Infiniband- und zwei Serial-ATA-Stecker-Komponenten nach außen. Die restlichen vier Transceiver als auch die insgesamt 61 LVDS-Leitungspaare benutzen vier impedanzdefinierte High-Speed-Buchsenleisten zwecks Erweiterung mit Aufsteckboards. Die zwei Infiniband-Steckverbinder sind nicht direkt an die Transceiver angebunden: Die sichere und problemlose Datenübertragung über längere Kabelverbindungen (bis 17 m) gewährleisten adaptive Kabel-Treiber und -Equalizer.

Wer sich jetzt fragt, wozu eine solch riesige Übertragungsrate benötigt wird, braucht sich nur den Anforderungswunschzettel seiner derzeitigen, respek-

tive potenziellen künftigen Kunden für die nächsten Jahre schicken zu lassen. Wohl dem, der auch für die nächsten Jahre mit moderaten Übertragungsraten auskommen möchte. Das rettet solche Glückspilze aber nicht vor der Flankensteilheit der Signale und vor den Störeinträgen durch die Stromversorgungs-Pins der Chips; der Fantasie hochinnovativer Halbleiterhersteller die Grenzen der Halbleiterphysik weiter auszuloten sind sichtlich kaum Grenzen gesetzt.

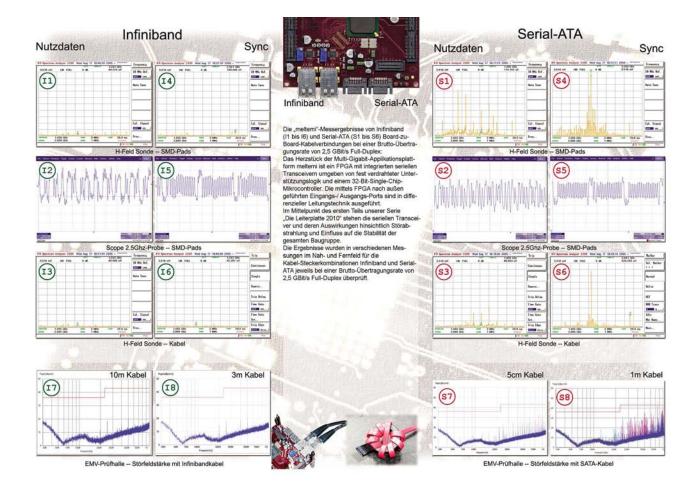

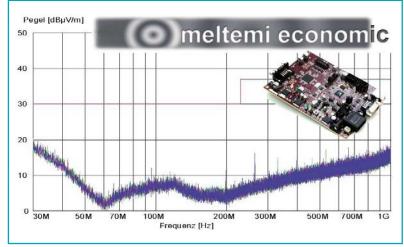

#### Auswirkungen der seriellen Transceiver hinsichtlich Störabstrahlung und Stabilität

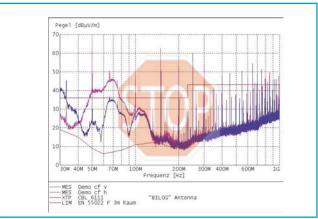

Schwerpunkte unseres Beitrages sind die seriellen Transceiver mit den unvermeidlichen Auswirkungen auf ihre Umgebung hinsichtlich Störabstrahlung und ihres Einflusses auf die Stabilität der restlichen Hardware. Den Kern bildet ein Vergleich verschiedener Messungen im Nah- und Fernfeld für zwei unterschiedliche Kabel-Stecker-Kombinationen, und zwar Infiniband als qualitativ hochwertige, aber kostenintensivere Lösung, sowie Serial-ATA als preiswertere, jedoch dem PC nahe stehende Variante. In beiden Fällen beträgt die Brutto-Übertragungsrate 2,5 GBit/s, Full-Duplex.

Für das Link-Layer-Protokoll wurde Aurora von Xilinx herangezogen. Es ist ein relativ leicht zu bedienendes Verfahren für Punkt-zu-Punkt-Verbindungen. Für Messungen im Nahfeld kam eine H-Feld-Sonde unseres Partners Dirks Corporate Consulting zum Einsatz (Bezugsquellen siehe Literaturhinweise am Schluss des Artikels). Fernfeldmessungen in der EMV-Prüfhalle im TGM-Wien dienten der Verifikation der im Labor durchgeführten Messungen.

Die "meltemi"-Messergebnisse von Inifiniband (I1 bis I6) und Serial-ATA (S1 bis S6) Board-zu-Board-Kabel-Verbindungen sind auf Seite 10 auf einen Blick dargestellt. Die Kabellänge für Infiniband ist mit 10 m und für Serial-ATA mit 1 m spezifiziert. Gemessen wurde mit Nutzdaten (I1 bis I3, S1 bis S3) und ohne Nutzdaten (14 bis 16, S4 bis S6). Als Messpunkte für die H-Feldsonde wurden die SMD-Pads (I1, I4; S1, S4) der jeweiligen Stecker auf der Leiterplatte und der Übergang Kabelstecker auf Kabelanfang (I3, I6; S3, S6) herangezogen. Die Darstellung und Speicherung der Daten im Zeitbereich (I2, I5; S2, S5) übernahm das 6-GHz-Oszilloskop (WaveMaster 8600A von LeCroy). Die Auswertung der Messkurven verdeutlicht erhebliche Unterschiede der Störabstrahlung von Infiniband- und Serial-ATA-Steckern und Kabeln. Trotz einer Kabellänge von 10 m für Infiniband und zusätzlichem Einsatz adaptiver Kabel-Equalizer lassen sich signifikante Abstrahlwerte weder im Nahfeld (I1, I4, I3, I6) noch in der EMV-Prüfhalle (17 – Kabellänge 10 m, 18 – Kabellänge 3 m) eruieren.

#### Korrekt konstruiertes und entkoppeltes Stromversorgungssystem zeigt Wirkung

Dramatisch sieht es allerdings für die Serial-ATA-Verbindung mit einer Kabellänge von 1 m sowohl im Nahfeld (S1, S4, S3, S6) als auch in der EMV-Prüfhalle (S8 – Kabellänge 1 m; S7 – Kabellänge 5 cm) aus. Erst bei einer sehr kurzen (5 cm) Serial-ATA-Kabel-Verbindung (S7) "normalisieren" sich die Störabstrahlwerte. Verantwortlich sind massive Impedanz-Fehlanpassungen und unzulängliche Schirmungen der Serial-ATA Stecker-Kabel-Kombination. Mit für Kabel geeigneten Ferrit-Konstrukten, die nachträglich angebracht werden können, lassen sich die Abstrahlwerte etwas reduzieren. Dass diese Möglichkeit überhaupt besteht, ist hauptsächlich der breitbandigen Stromver-

#### **60 Entwickler in** jeder Box.

Unser Team von Programmierern hat in über 100.000 Arbeitsstunden pro Jahr die Matrox Imaging Library (MIL) entwickelt. Wir haben unsere Arbeit getan, damit Sie sich auf die Erstellung Ihrer Anwendung konzentrieren können.

Unsere praxiserprobte industrielle und wissenschaftliche Bildverarbeitungsbibliothek:

- bietet eine einheitliche Programmierschnittstelle mit Unterstützung der gesamten Hardwarepalette von Matrox Imaging

- wurde direkt von Matrox für die Verwendung der Intel® MMX™/SSE/SSE2 Technologie optimiert

- entlastet transparent mit der ASIC/FPGA-basierten Matrox Verarbeitungshardware

- läuft unter Microsoft® Windows® oder Linux

Bestellen Sie Ihre kostenlose 30-tägige MIL Demo-CD: www.matrox.com/imaging/de/ produkte/mil/home.cfm

#### >> Nehmen Sie heute noch Kontakt zu uns auf!

089/621 70-520 imaging.infogermany@matrox.com www.matrox.com/imaging/de

sorgungs-Entkopplung mit gestapelten Stromversorgungsflächen zuzuschreiben. Wie anschaulich aus der Messung S7 (EMV-Prüfhalle) zu entnehmen ist, reduzieren sich die Abstrahlwerte bereits bei einer Kabellänge von 5 cm deutlich und erreichen bei noch weiterer Reduktion "Infiniband-Werte". Ein deutlicher Beweis für die herausragenden Eigenschaften von Boards mit korrekt konstruierten und entkoppelten Stromversorgungssystemen.

Anmerkung zu den Bildern I1, I3, I4 und I6 für die Infiniband-Kabelverbindung: Es handelt sich hier keinesfalls um platzraubende Kopien ein und derselben Messung. Es war schlicht und ergreifend einfach NICHTS Brauchbares an Abstrahlung zu messen(!). Die wenigen "Zacken" in der Kurve sind eher anderen Störsendern wie "Handymasten" zuzuordnen. Eine aus Sicht des Verfassers und erst recht aus Sicht des Lesers "enttäuschende" Grafik, die nur gähnende Langeweile hervorrufen kann. Daraus zu vermuten, die Serial-ATA-Kabelverbindung mit ihren "erfrischend auffälligen" Messkurven wäre bewusst nur als Rechtfertigung für diesen Vergleich schaltungstechnisch "hinaufkonstruiert" worden, entbehrt jeglicher Grundlage. Andererseits, als diametralen Widerpart um im geneigten Leser Spannung zu erzeugen nimmt sie der Autor dankbar an. Doch welche Hinweise stecken tatsächlich in diesen Kurven (S1, S4, S3, S6)? Was lässt sich daraus Brauchbares heraussieben? Zuerst einmal die unerfreuliche Erkenntnis, dass bei fehlenden Nutzdaten (S4, S6; aus Sicht des Anwenders sollte eigentlich gar nichts übertragen werden) die Abstrahlwerte bei der Basisfrequenz von 1,25 GHz ein Maximum erreichen. Dies liegt darin begründet, dass normalerweise diese Basisfrequenz zur Synchronisation der FPGA-Transceiver Empfänger-Hardware benötigt wird, um keine unakzeptabel langen Aufsyn-

#### Kosten und Nutzen von Kabelverbindungstechniken

chronisationszeiten entstehen zu lassen.

Wenn man Pech hat fliegt man durch simples Nichtstun (keine Nutzdaten) erst recht durch die EMV-Prüfung. Manche Hardwareentwickler behaupten, dass dies der eigentliche Grund für die hohe Zahl an Wiederholungsprüfungen in den EMV-Messhallen wäre, indem sie auf die Tatsache verweisen, dass die meisten Prüflinge überhaupt weder FPGAs noch serielle Hochgeschwindigkeits-Transceiver auf der Leiterplatte hätten. Vor so viel Sarkasmus distanziert sich der Autor allerdings entschieden.

Beim Verwenden von Kabel-Verbindungstechniken für Übertragungsraten im Multi-GigaBit/s-Bereich, besonders im industriellen Umfeld, gilt es Kosten und Nutzen sorgfältig gegeneinander abzu-

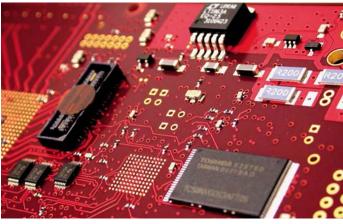

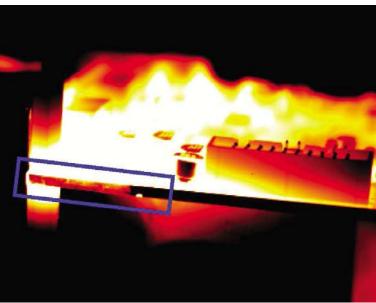

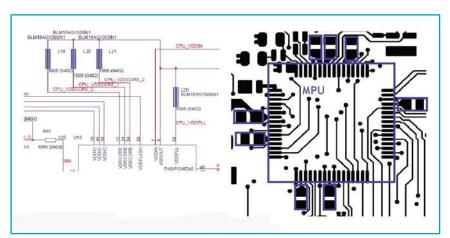

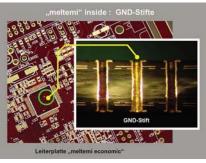

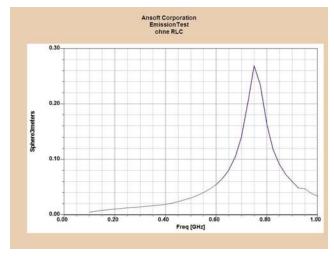

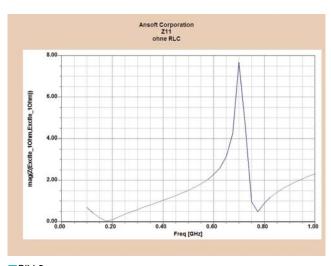

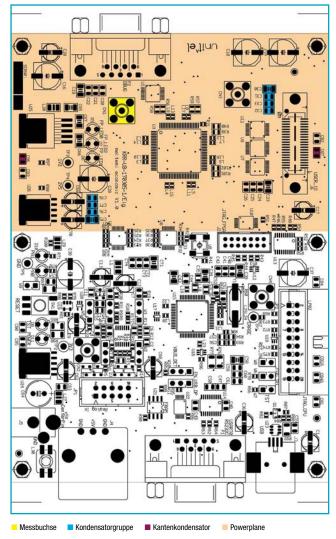

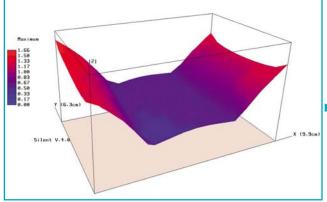

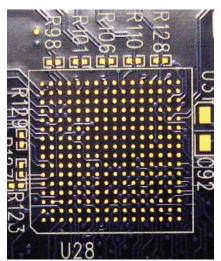

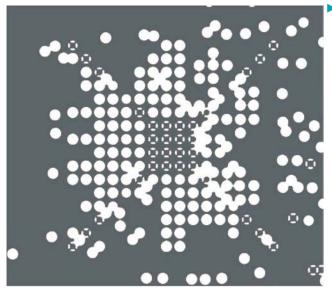

■Bild 3: Flächige entkoppelte Stromversorgungsebenen sind im Lagenaufbau integriert

wägen. Das Beispiel Serial-ATA-Verbindungstechnik mit erheblich höheren Störabstrahlwerten zwingt den Hardwareentwickler zu einem umfassenderen und zeitraubenderen Studium von Lösungsansätzen in vielen, künftig übergreifenden Wissensgebieten. Das widerspricht der derzeit globalen Marktdoktrin immer leistungsfähigere Hardware in immer kürzeren Zeitabständen serienreif zu entwickeln und termingerecht in den entsprechenden Marktfenstern zu positionieren. Langfristige Kooperationen und Partnerschaften werden immer wichtiger, zumal die Grundlagenforschung durch die Bank aufwändiger wird. Doch prüfe, wer sich ewig bindet.

#### Gartenzäune und andere Kalamitäten

Entwickler, die sich mit High-Speed-Technologien herumschlagen müssen, also in naher Zukunft praktisch alle, denen zusätzlich die hohe Ehre zuteil wurde, FPGAs mit schnellen seriellen Transcei-

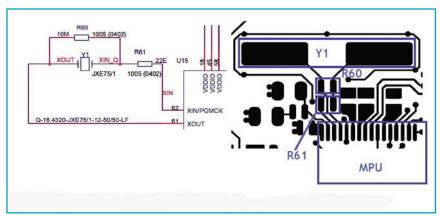

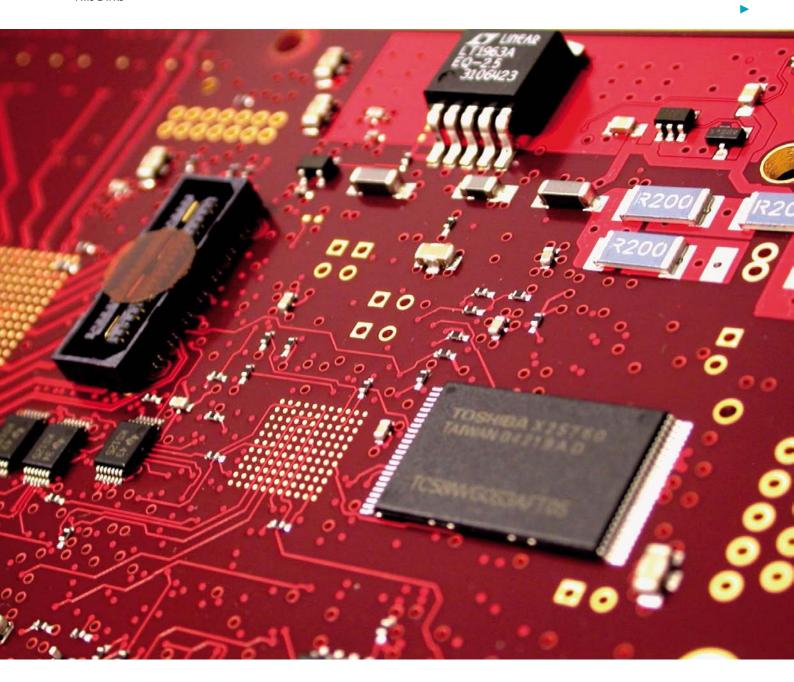

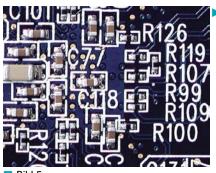

▲ Bild 1: Blockschaltbild und bestücktes meltemi-Board: Mittelpunkt ist ein FPGA mit integrierten seriellen Transceivern, umgeben von fest verdrahteter Unterstützungslogik und 32-Bit-MCU

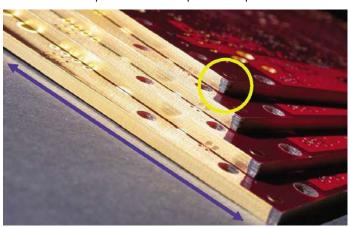

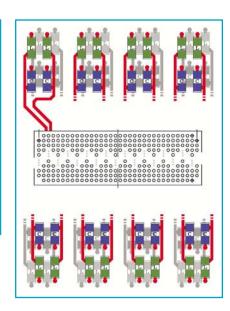

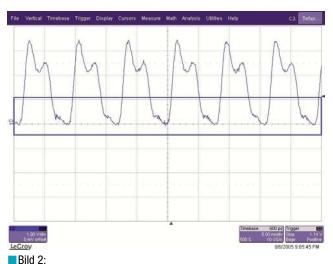

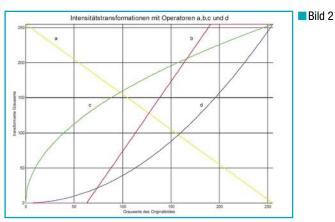

▶ Bild 2: "Gartenzaun" für 8 Transceiver auf Ober- und Unterseite: Das Ergebnis hinsichtlich Verbesserung der Signalintegrität zwecks störarmer Datenübertragung ist nahezu unbrauchbar.

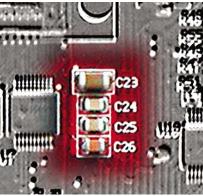

vern auf ihren Leiterplatten ihr Eigen nennen zu dürfen, werden anfangs die seltsam anmutenden Drossel-Kondensator-Konstrukte zur "Entstörung" der Transceiver-Stromversorgungspins misstrauisch beäugt haben. Bei 8 Transceivern braucht man immerhin 32 Drosseln und ebenso viele Kondensatoren (Bild 2). Aber so richtig schöne "Gartenzäune" bekommt man bei 24 Transceivern. Für jeden Leiterplattenlayouter ein Horror-Szenario hinsichtlich Platzierung, Einhaltung der Regeln für differenzielle Leitungsführung und zahlreicher weiterer Maßnahmen zur Verbesserung der Signalintegrität zwecks stabiler, möglichst störarmer Datenübertragung.

Der Aufwand, um all dies unter einen Hut zu bringen, ist enorm. Das Ergebnis bleibt kümmerlich bis unbrauchbar. Weil hier der korrekten breitbandigen Stromversorgungsentkopplung einfach NICHT Genüge getan wurde. Trotzdem wird diese Gartenzaun-Lösung "zwingend" in den Datenblättern und Applikationsnoten vorgeschrieben – nicht einfach nur vorgeschlagen.

Was bietet der Verursacher, der Halbleiterhersteller, sonst noch an? Bis auf weni-

ge Ausnahmen die gute alte Stützkondensator-Lösung mit meist 100 nF SMD-Kondensatoren.

Bei den zu erwartenden hohen Schaltfrequenzen ist der Wirkungsgrad einer solchen Stützung zuverlässig mit praktisch null anzusetzen – eine leicht zu merkende Faustformel.

Viel Hilfe kann man also nicht erwarten. Vernünftiger wäre, auf diese Gartenzäune von vornherein zu verzichten (Bild 2) und sie komplett wegzulassen (Anmerkung: Es gibt allerdings Lösungsvorschläge, wo man sie doch wieder benötigt, aber dann nutzen sie auch etwas). So einfach ist es allerdings nicht, denn sie wurden nicht ohne zwingenden Grund den Board-Designern aufoktroyiert.

#### Breitbandig entkoppelte Stromversorgungsebenen

Über eine Art Tauschhandel kann der Physik jedoch Genüge getan werden: Statt Unmengen an Drosseln, Kondensatoren und Einzelleitungen werden flächige, geschickt über Kondensatorgruppen breitbandig entkoppelte Stromversorgungsebenen in bestimmter Anordnung in den Leiterplatten-Lagenaufbau integriert.

Im Applikations-Board "meltemi" wurde ein solcher Lagenaufbau realisiert und harten Prüfungen unterworfen. Die Resultate können sich sehen lassen: Sowohl hinsichtlich der Störabstrahlwerte im Nahfeld als auch im Fernfeld erzielt die Leiterplatte hervorragende Ergebnisse. Ebenso ließen sich mit der Infiniband Kabel-Stecker-Kombination bei Übertragungsraten von 2,5 GBit/s und einer Kabellänge von 10 m (auch bei zwei parallel betriebenen Kanälen – also 5 GBit/s) keine Übertragungsfehler feststellen. (cm) Literatur:

RocketIO™ Transceiver User Guide UG024 (v2.5) December 9, 2004, Virtex-II Pro, Xilinx,

Virtex-II Pro and Virtex-II Pro X FPGA User Guide UG012 (v3.0), August 2004, Virtex-II Pro, Xilinx

Applikationsbericht uH-Feldsonde AC220, Allice Meßtechnik GmbH Wenn Leiterplatten strahlen, Prof Chr. Dirks

Vorteile dünner Substrate in Ground-/

Powerplane-Systemen, Prof. Chr. Dirks

Ilfa-Akademie

"meltemi"-Folder

#### Schnelle differenzielle Signale entflechten

## Die High-Speed-Regeln beachten

Moderne EDA-Software wartet mit vielen "hilfsbereiten"

Assistenten auf, um den Weg für ein 100%iges Routing-Ergebnis zu ebnen. Erfüllt dieses Ergebnis die physikalischen Randbedingungen der Hardware hinsichtlich Stabilität und EMV?

Tatsächlich kommt man ohne weitere tief greifende von Hand durchgeführte Optimierungen nicht zu den erhofften Ergebnissen. Im zweiten Kapitel schildern die Entwickler mit welchen Maßnahmen sich ein hoher Grad an Hardwarestabilität in Hochgeschwindigkeitsanwendungen erzielen lässt und welche Vorgehensweise sich beim Entflechten differenzieller Hochgeschwindigkeitssignale in der Praxis bewährt hat.

Gerhard Eigelsreiter

Das detaillierte Sichtbarmachen eines gedanklichen Bildes wird im Allgemeinen mit dem Begriff "Layout", aus dem Englischen: Anlage oder Plan, umschrieben. Die Erweiterung zum Wortungetüm "Leiterplattenlayout", auch "Leiterplattenentflechtung", wirkt nahezu anheimelnd vertraut im Vergleich zur entkomprimierten Version: "Für die Träger elektronischer Schaltwerke (die Leiterplatte) ergibt sich zwecks Erstellung von Fertigungsdaten die Notwendigkeit, die im Schaltplan zwischen den Anschlüssen von aktiven und passiven elektronischen Bauelementen abgebildeten Verbindungen in eine auf eine gedruckte Schaltung aufzutragende geometrische Form zu bringen". So umständlich und subtil wie diese Formulierung verhält es sich mit der Bedienung vieler Leiterplattenentflechtungs-Softwarepakete. An allen Ecken und Enden lauern "hilfsbereite" Assistenten um den Weg für ein 100%iges Routing-Ergebnis zu ebnen. Doch erfüllt dieses Ergebnis auch die physikalischen Randbedingungen der Hardware hinsichtlich Stabilität und EMV? Tatsächlich kommt man ohne weitere tief greifende per Hand durchgeführte Optimierungen nicht zu den erhofften

Resultaten. Das an sich klare gedankliche Lösungsbild droht in den Überlegungen und Tricks völlig zu versumpfen, um Softwareklippen zu umschiffen und reichlich vorhandene, selten abschaltbare Softwareassistenten in den Griff zu bekommen.

#### Interdisziplinäre Konstellationen von Experten

Die enorme Komplexität und damit Fehleranfälligkeit der Layout-Tools wird deshalb von vielen Herstellern mit dem Wunsch der Anwender begründet, dem Idealziel vom Knopfdruck-Design möglichst nahe zu kommen. Ein Ziel, dass infolge immer kürzerer Produktzyklen weiter denn je entfernt zu liegen scheint. Aus zeitlichen, folglich wirtschaftlichen Gründen reicht es nicht mehr aus, einige wenige Projektsegmente auszulagern. Es bedarf vielmehr einer wesentlich allgemeineren, interdisziplinären Konstellation von Spezialisten, Produktionsunternehmen und Dienstleistern. Einer Gruppierung, die den Bogen von der Grundlagenforschung bis zur Produktion in enger Verzahnung überspannt. Und die auch bereit ist, dieses Knowhow in jeder Phase der Projektentwicklung in

Form von praxisoptimierten Seminaren, begleitenden Beratungen oder kompletten Hardwareentwicklungen zur Verfügung zu stellen. Wer hier absolute Perfektion in allen Disziplinen erwartet, dem folgt die Enttäuschung auf dem Fuße. Der Forschungs- und Entwicklungsumfang wäre infolge des unverhältnismäßig hohen Zeitaufwands nicht zu rechtfertigen und aus wirtschaftlichen Gründen schon gar nicht vertretbar. Dennoch lassen sich ein erstaunlich hoher Grad an Hardwarestabilität in Hochgeschwindigkeits-Anwendungen errei-

chen und die dafür notwendigen Lösungen vermitteln. Dem Stiefkind Leiterplattenproduktion widmen sich intensiv unsere Partner in den kommenden Kapiteln.

## Übergang zu differenziellen Verbindungstechniken

Betrachtet man gängige Layouts gegenwärtiger Leiterplatten, so bilden unsymmetrische (Single-Ended) Leiterbahnverbindungen nach wie vor die überwiegende Basis zum Transport

## **NEXT Generation Cadence® Allegro® PCB Design Plattform**

Erleben Sie die nächsten Allegro Generationen am 15. Mai in München auf der CDNLive! EMEA 2007

Beim FlowCAD PCB Tag anläßlich CDNLive! EMEA 2007 in München können Sie erleben, wie Cadence zukünftig neue Standards im PCB Design setzt.

Nutzen Sie die Gelegenheit sich mit anderen PCB Designern über Steigerungen Ihrer Produktivität auszutauschen.

Die Präsentation wird hauptsächlich auf Deutsch gehalten.

Melden Sie sich kostenlos an unter:

www.FlowCAD.de/cdnlive

Cadence and Allegro are registered trademarks of Cadence Design Systems, Inc.

FlowCAD is a Cadence Channel Partner and the sponsor of the PCB Day at CDNLive! EMEA 2007.

von Hochgeschwindigkeitssignalen. Eine wachsende Fülle damit verbundener Probleme hinsichtlich Signalintegrität, speziell "Ground Bouncing, sind die negativen Begleiterscheinungen. Es wird zwar den direkten Signalverbindungen (Hinstrom) alle Aufmerksamkeit zuteil, jedoch den Rückstrompfaden (Masse oder Masseleitungen) keinerlei Beachtung im Layout geschenkt. Die Folgen sind zunehmende Instabilitäten und Funktionsstörungen der gesamten Hardware. Dies gilt in besonderem Maße der breitbandigen Stromversorgungsentkopplung, die inzwischen untrennbar mit stabiler Gerätefunktionalität einhergeht.

Welche Gründe stehen diesem längst überfälligen "Paradigmenwechsel", dem Übergang zu differenziellen Verbindungstechniken, entgegen? Auf rein logischer Ebene betrachtet: Keine! Na also, könnte man jetzt denken, her mit der neuen Technik. Leidgeprüfte, erfahrene Layouter werden spätestens hier heftig abwinken. Und in der Tat, das Misstrauen erweist sich mehr als gerechtfertigt.

Differenzielle Leitungsführungen werden von einer Vielzahl an Regeln und Maßnahmen begleitet, die umfangreiche Veränderungen an bisher gewohnten Lösungsmethoden erfordern. Dies haben die EDA-Tool-Hersteller ebenfalls seit geraumer Zeit erkannt und reagieren mit Zusatzfunktionen und -optionen in ihren Softwareupdates. Trotz allem bleibt immer noch viel zu viel Spielraum für interaktive Eingriffe übrig.

### PCIe fordert bei 2,5 GBit/s Ubertragungsrate maximale Längenunterschiede von 0,1 mm

Ein Auszug der geforderten Maßnahmen und einzuhaltenden Regeln soll mehr Licht ins Dunkle bringen:

1.) LVDS (Low Voltage Differential Signaling) bedingt zwei nebeneinander, manchmal auch übereinander laufende Leitungspfade in bestimmten vorher zu definierenden geometrischen Abständen zueinander. Diese Abstände müssen mit der gewünschten Terminierung (üblicherweise 100  $\Omega$ ) korrelieren. 2.) Abhängig von der Höhe der Übertragungsgeschwindigkeit dürfen die Leitungslängenunterschiede innerhalb der differenziellen Paare bestimmte Werte nicht überschreiten. Bis 1 GBit/s sollten die Längen um nicht mehr als 0,5 mm differieren. PCle fordert bei 2,5 GBit/s Übertragungsrate maximale Längenunterschiede von 0,1 mm!

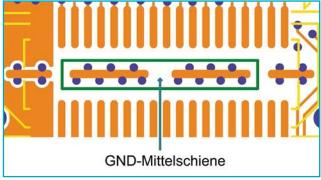

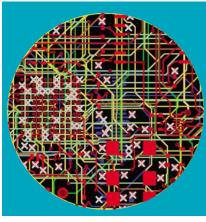

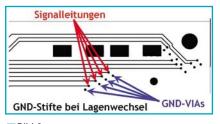

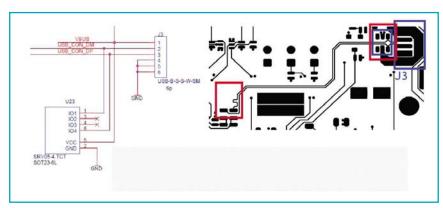

Bild 1:

Leitungsführungen von differenziellen und "Single-Ended"-Signalen. Alle Leitungen sind gemeinsam über ein und denselben mit 50  $\Omega$  Impedanz (gegen GND) ausgelegten Stecker geführt.

Bild 2:

Die Pads (im grünen Rechteck) der GND-Schiene dieser Steckerkonstruktion sind mit etlichen Vias (blaue Punkte) an die innen liegenden GND-Flächen angebunden. Schlitzbildungen in Vcc-Flächen durch zu eng aneinander gereihte GND-Vias (blaue Punkte) sind jedoch unbedingt zu vermeiden.

Bild 3:

Layout-Auszug vom Längenausgleich (grünes Rechteck) von differenziellen Leitungspaaren. Bei sehr schnellen Übertragungsraten (mehrere GBit/s) ist dieser Ausgleich segmentweise durchzuführen.

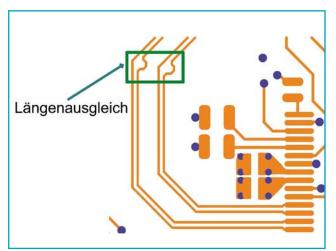

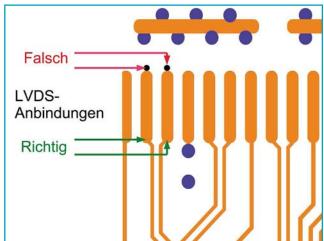

Bild 4

Zwecks Vermeidung von Leitungsstubs (ins Leere gehende Leitungssegmente) muss auf der korrekten Padseite (Konstruktion des Steckverbinders beachten) angebunden werden. Hier ein Beispiel für den QSE-020-01-L-D-A von Samtec.

3.) Impedanz-Änderungen innerhalb der Übertragungsstrecke sind zu meiden respektive zu minimieren. Unvermeidliche Lagenwechsel lassen sich mittels symmetrischer Via-Paare lösen. Ideal sind Via-Paare mit lediglich moderaten Impedanzänderungen (impedanzdefinierte Vias). Zur Bestimmung der geometrischen Werte der zusätzlichen GND-Vias müssen geeignete Software-Tools herangezogen werden.

- 4.) Die Abstände zwischen differenziellen Leitungspaaren sollten mindestens den 5-fachen Wert des Innen-Abstandes eines solchen Leitungspaares erreichen um Impedanzverzerrungen und Übersprechen zu minimieren. Dies gilt ebenso für benachbarte "Single-Ended" -TTL-Leitungen.

- 5.) Das Füllen von Freiräumen mittels Masseflächen wirkt impedanzändernd und hat zu unterbleiben.

#### Rückstrom nah zum Hinstrom führen

Als Nachteil differenzieller Übertragungsverfahren wird besonders häufig die doppelte Anzahl zu verlegender Leitungen angeführt. Dies ist insofern bedenklich, weil hier die wichtigste Merkregel: "Der Rückstrom ist so nahe wie möglich zum Hinstrom zu führen" bereits in der Vergangenheit bei TTL-Verbindungen (Single Ended) völlig ianoriert wurde. Um es klarer zu formulieren: Die Rückstromleitung wurde schlichtweg durch das GND-Symbol im Schaltplan ersetzt und im Layout als lästige Masseleitung oder bestenfalls halbherzige Massefläche mit vielen Schlitzen realisiert. ES GIBT ABER KEINE MASSE-FLÄCHE ODER MASSELEITUNG MIT DER IDEAL-IMPEDANZ von 0 Ol Deswegen sind die Ausdrücke

Masse oder Massefläche durch den Begriff Rückstromleitungen schleunigst zu er-

noch den Hauch einer Chance haben einigermaßen glimpflich durch die EMV-Prüfung zu kommen, ganz zu schweigen von stabiler Hardwarefunktionalität Als Vorteile differenzieller

Übertragungsverfahren sind neben hoher Störsicherheit und geringen Spannungshüben (ca. 350 mV bei LVDS)

setzen, will man in Zukunft

vorzugsweise das fast völlige Fehlen von Ground-Bouncing-Effekten sowie Übertragungsraten >10 GBit/s erwähnenswert. Als nachteilig wird derzeitig der hohe Aufwand in der Layoutumsetzung bedingt durch komplexe Regelwerke und vermehrter Einsätze interaktiver Routingstrategien empfunden. Die Unterstützung durch geeignete

Werkzeuge hinkt derzeit weit, häufig in kaum erträglichen Ausmaßen, hinterher. Unterm Strich überwiegen dennoch die Vorteile hinsichtlich EMV und Signalintegrität bei Weitem. Beispiele für die korrekte An-

bindung impedanzdefinierter Stecker und differenzieller Leitungsführungen zeigen die Bilder 1 bis 4.

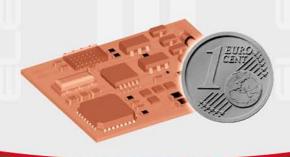

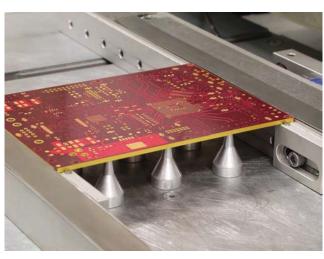

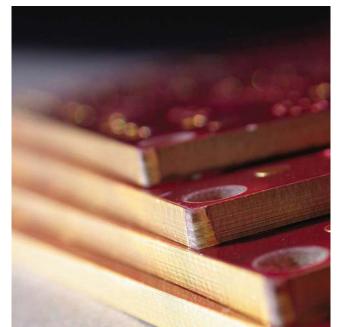

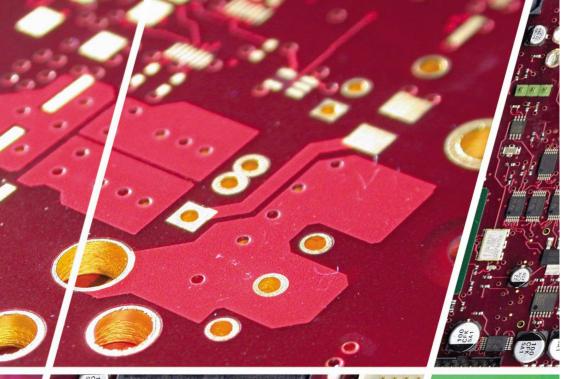

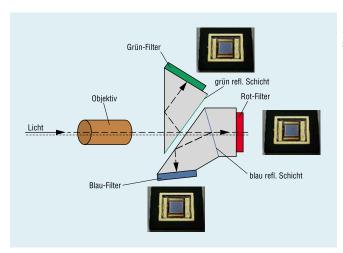

Die physikalischen Eigenschaften revolutioniert

## Metallisierung der Leiterplattenkanten

Eine Besonderheit der meltemi-Leiterplatte ist die Kantenkontaktierung (oder auch Kantenmetallisierung). Die Kantenkontaktierung bringt für Baugruppen mit mittlerem bis hohem Anspruch an EMV, Signalintegrität und Entwärmung deutlich messbare Vorteile bei vergleichsweise vernachlässigbaren Kosten. Die Praxis hat bewiesen, dass sich die Theorie umsetzen lässt und funktioniert.

#### **Arnold Wiemers**

Eine Baugruppe funktioniert unter EMV-Aspekten stabil, wenn sie keine eigene Störstrahlung abgibt (Emission) und wenn sie nicht auf Störungen durch fremde Baugruppen (Immission) reagiert.

Technisch gesehen ergeben sich diese Störungen durch die Signalübertragung zwischen den Komponenten einer Baugruppe oder zwischen mehreren Baugruppen eines Gerätesystems. Die zielgerichtete Signalübertragung auf komplexen Multilayersystemen findet mittels der Leiterbahnen statt. Die Stromversorgung erfolgt über flächige Ebenen. Berücksichtigt werden muss, dass für jede Signalübertragung natürlich auch eine Rückleitung vorhanden sein muss (die sogenannte GND-Plane), und dass der Informationstransport nicht in zweidimensionalen Paketen, sondern in dreidimensionalen elektromagnetischen Feldern stattfindet. Damit ist jede Baugruppe (und jede Leiterplatte) ein gigantischer elektronischer Mikrokosmos mit einer

kaum vorstellbaren Ereignisvielfalt auf kleinstem Raum.

Hier liegt der Schlüssel für eine erweiterte Strategie zur Erlangung der EMV-Stabilität. Der Aufbau eines Multilayers besteht in der Übereinanderschichtung von Signallagen und Powerplanes. Beim Betrieb einer Baugruppe wird erzeugte, aber nicht benötigte Energie über den Kantenbereich der Powerplanes abgestrahlt. Das Schaltungskonzept bemüht sich, diese Effekte zu kompensieren, beispielsweise durch die Signalterminierung, durch definierte Leitungseigenschaften (Impedanz) oder durch hochkapazitive Multi-Power-Systeme (= MPS). Der Erfolg dieser linearen Signalübertragung kann nicht vollständig sein. Es fehlt eine effektive Kontrolle der elektromagnetischen Felder im dreidimensionalen Raum der Leiterplatte.

Eine Kontrolle kann jedoch erreicht werden, wenn eine Kompartimentierung der Feldbereiche auf und in einer Leiterplatte stattfindet. Im Prinzip kann diese Kompartimentierung durch eine strukturierte Abschirmung erfolgen.

Die Analyse eines Multilayer-Aufbaus ergibt die einfache Erkenntnis, dass jede Lage rechtwinklig an der Kante der Leiterplatte endet.

Damit ist die Aufgabe definiert: Die Kontrolle der dreidimensionalen elektromagnetischen Räume auf einer Leiterplatte ergibt sich durch die Abschirmung an der Kante der Leiterplatte. Die Prognose ist, dass sich dadurch das EMV-Verhalten einer Leiterplatte/Baugruppe erheblich verbessert.

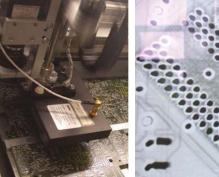

■ Das Kontaktieren von Leiterplatten Um die Funktion der Abschirmung einschätzen zu können, muss die galvanotechnische Kontaktierung erläutert werden. Der Prozessschritt des Kontaktierens ist elementar für die Herstellung von Leiterplatten. Die galvanotechnische Verbindung mehrerer Ebenen einer Leiterplatte erfolgt an der Innenwandung von Bohrungen vermittels eines kathodischanodischen Verfahrens zur Kupferabscheidung.

Topologisch gesehen gehört die Innenwandung einer Bohrung zur Oberfläche der Leiterplatte. Das Verfahren der galvanotechnischen Kontaktierung führt also grundsätzlich zu einer metallischen Abscheidung auf der Leiterplattenoberfläche. Diese Oberfläche kann auf unterschiedlichste Art durch Bohrungen, Schlitze oder Fräsungen modifiziert werden.

Soll die spätere Leiterplattenkante metal-

lisiert werden, dann ergibt sich für die Herstellung der Leiterplatte vornehmlich eine geringfügige logistische Umstellung der Prozessabläufe. Die zu metallisierende Kontur darf nicht (wie üblich) erst in einem der letzten Arbeitsschritte gefertigt werden, sondern muss bereits vor dem Kontaktieren ausgeführt worden sein

Für die Bearbeitung der Kontur empfehlen sich Fräswerkzeuge. Mit diesen Werkzeugen sind gerade oder runde Konturen problemlos ausführbar. Es können Innenausschnitte und/oder Teilbereiche der Kontur strukturiert werden. Die Konturfräsung kann die Kante über die gesamte Dicke der Leiterplatte freistellen. Es sind aber auch kontaktierbare Niveaufräsungen machbar, die nur eine vorgege-

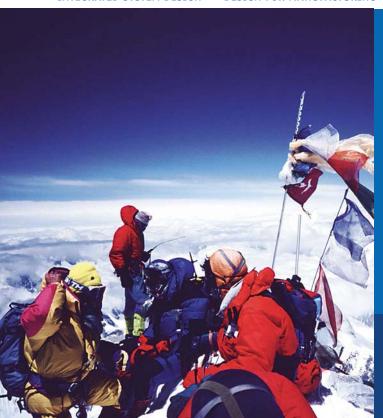

## SIE WOLLEN AN DIE SPITZE - WIR HELFEN IHNEN BEIM AUFSTIEG!

INTEGRATED SYSTEM DESIGN + DESIGN FOR MANUFACTURING + ELECTRONIC SYSTEM LEVEL DESIGN + FUNCTIONAL VERIFICATION

**Expedition**<sup>TM</sup> **Enterprise** | Spitzen-Unternehmen werden Ihnen bestätigen, dass Sie nur mit Zielstrebigkeit, Engagement und Innovationen ganz an die Spitze gelangen. Mentor Graphics konsequente Investition sichert marktführende Produkte.

Unsere Expedition<sup>™</sup> Enterprise Lösung verkürzt deutlich Designzyklen durch den wirksameren Einsatz der Ressourcen interdisziplinärer Designteams und senkt die Kosten durch ein verbessertes Supply Chain Management. Differenzieren Sie sich und Ihr Team mit einer Lösung, die fortschrittlichste Design- und Fertigungs-Technologien unterstützt. Erfahren Sie mehr unter www.mentor.com/expedition

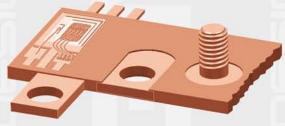

Bild 1: Die Kanten aller kontaktierten Konturfräsungen haben auf der fertigen Leiterplatte die gleiche galvanische Endoberfläche wie die eigentliche

Eine kompakte Fläche auf einer Leiterplattenseite erreicht nie die Wärmespreizung und Wärmeabstrahlung wie ein um die Kante laufendes flächiges Band

bene Solltiefe freistellen. Bei umlaufender Kantenkontaktierung muss beachtet werden, dass für die weiteren Fertigungsschritte der Leiterplatte 1 bis 2 mm breite Haltestege zum Produktionsnutzen bleiben müssen, die ohne weiteres nicht kontaktiert werden können.

Die Kanten aller kontaktierten Konturfräsungen haben auf der fertigen Leiterplatte die gleiche galvanische Endoberfläche wie die eigentliche Leiterplatte auch (Bild 1).

Die Fertigungskosten für die Kantenkontaktierung sind gering. Jeder Hersteller von kontaktierten Leiterplatten verfügt über einen Galvanoautomaten und eine Fräsmaschine. Es sind also keine zusätzlichen Investitionen in Maschinen oder Prozesse erforderlich. Lediglich in den Fertigungsabläufen muss eine Fallunterscheidung nach "Kantenkontaktierung: ja/nein" möglich

#### Entwärmung

Ursprünglich war ein kontrollierteres EMV-Verhalten die Motivation für die Kantenkontaktierung. Es war bald offensichtlich, dass auch die aktive Entwärmung einer Leiterplatte bei kontaktierten Kanten deutlich besser ist.

Die Entwicklung immer leistungsfähigerer Elektronik auf immer kleinerem Raum führt zwangsläufig zu Wärmeproblemen. Die Ableitung der Wärme durch Kühlkörper oder Gehäuse ist aufwändig und verteuert die Gerätekosten. Eines der strategischen Ziele für das CAD-Layout und die Baugruppenkonstruktion muß deshalb die Integration der Entwärmung in das Multilayersystem sein. Zusätzlich zu diversen konstruktiven Eigenschaften eines Multilayers (Dickkupferschichten, MPS) muss das Leiterbild in die Entwärmung einbezogen werden. Dass die Kantenkontaktierung hier keineswegs nur einen trivialen Beitrag leisten kann, folgert aus der Berechnung der Kantenoberfläche einer Standard-Europakarte. Es ergibt sich eine Kantenfläche von  $2 \cdot (10 + 16) \cdot 0.15 = 7.80 \text{ cm}^2$ .

Diese Nettofläche kann heute bei kompakten Layouts auf den Außenlagen einer Leiterplatte kaum für die Entwärmung freigehalten werden.

Ergänzend muss die Qualität der Entwärmung über die Kontaktierung der Leiterplattenkante bewertet werden. Eine kompakte Fläche auf einer Leiterplattenseite hat nie die Wärmespreizung und Wärmeabstrahlung wie ein um die Kante laufendes flächiges Band (Bild 2).

#### Signalintegrität

Die Bauteilindustrie hat bereits akzeptiert, dass mit der Kantenkontaktierung im Prinzip auch ein Vorteil für die Signalintegrität bei der Signalübergabe von der Baugruppe an die Peripherie entsteht.

Für jedes anspruchsvolle elektronische System (Beispiel: LVDS, High-Speed) ist die Schnittstelle von der Baugruppe zum Kabel und/oder zum Stecker eine Schwachstelle. Hier fehlt für wenige Millimeter auf der Strecke von der Leiterplattenkante bis zum Kabel die Abschirmung oder der durchgehend zuverlässige Massebezug für die Signalübertragung. Deutliche Störungen der Signalqualität können die Folge sein.

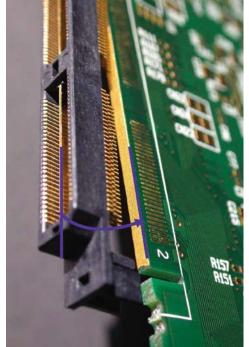

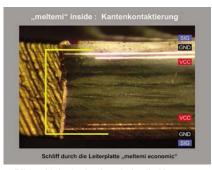

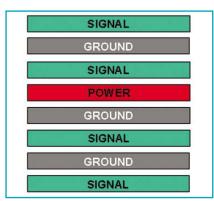

Die Signalintegrität an dieser Schnittstelle kann sichergestellt werden, wenn Leiterplatte, Stecker und Kabel eine funktionelle Einheit bilden. Diese Aufgabe wird mit Steckern gelöst, die auf die kontaktierte Kante einer Leiterplatte aufgesetzt werden. Im oberen und unteren Bereich des Steckers erfolgt die Kontaktübergabe der differenziellen Signale an die obere und untere Seite der Leiterplatte. Im Mittenbereich hat der Stecker eine metallische Trennfläche, die gleichzeitig als Referenzplane dient. Rückseitig ist diese Trennfläche mit der partiell metallisierten Kante der Leiterplatte verbunden (Bild 3).

Bild 3:

Im Mittenbereich hat der Stecker eine metallische Trennfläche, die als Referenzplane dient. Rückseitig ist diese Trennfläche mit der partiell metallisierten Leiterplattenkante verbunden.

Im Idealfall sieht dadurch jedes Signal vom Kabel über den Stecker bis zum Eingangsbaustein auf der Leiterplatte ein homogenes elektromagnetisches Umfeld.

#### Das Ergebnis

Die Kantenkontaktierung bringt für Baugruppen mit mittlerem bis hohem Anspruch an EMV, Signalintegrität und Entwärmung deutlich messbare Vorteile bei vergleichsweise vernachlässigbaren Kosten. Die EMV-Stabilität von meltemi ist beeindruckend. Und das Zitat aus dem Prüflabor: "Die Sonde muss defekt sein. Ich messe nichts.", ist bereits legendär. (cm)

#### **Aufbruch in die dritte Dimension**

Man sollte erwarten, dass längst alles durchdacht ist. Zumindest, was die Leiterplattentechnologie betrifft. HDI (High Density Interconnection) und Laservias haben wir hinter uns, die Mikrofeinstleitertechnik (MFT) vor uns, aber das ist letztlich alles nur Mechanik. Kleiner, feiner, preiswerter sind die Maximen der Leiterplattentechnologie. Wer spricht vor diesem Hintergrund von sensationellen Ergebnissen, die sich für die elektrophysikalischen Eigenschaften von Leiterplatten ergeben? Manchmal sind Lösungen simpel und die Frage ist erlaubt, warum niemand eher darauf gekommen ist. Wahrscheinlich haben die Philosophen unter den Kryptographen recht, die meinen, "dass nichts so verborgen ist, wie das Offensichtliche". Wer täglich mit Leiterplatten umgeht, weiß, dass es eine "Bestückungsseite" und eine "Lötseite" gibt, manchmal auch "TopLayer" und "BottomLayer" oder "Primärseite" und "Sekundärseite" genannt. Hat eine Leiterplatte noch mehr Ebenen, dann werden auch diese akribisch und zweifelsfrei durchgezählt und bekommen einen Namen. Die dritte Dimension der Leiterplatte, die umlaufende Kante, hat keinen Namen. Für die Kante hat sich bisher kaum iemand interessiert. Das wird sich künftig ändern.

Systeme für professionelle Elektronik und Automation

Tel.: 064 04 / 697-0 Fax: 064 04 / 697-120

E-Mail: spea@spea-ate.de

SPEA GmbH

Ruhberg 2

D-35463 Fernwald

www.spea-ate.de

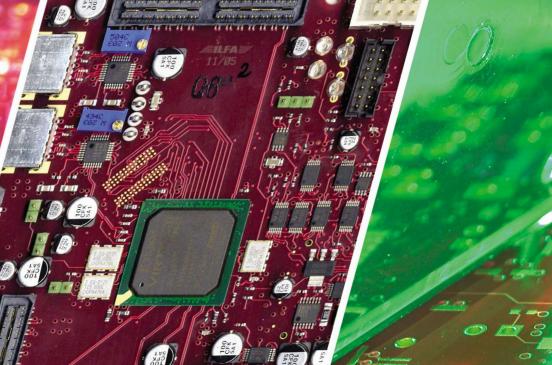

#### Was moderne Multilayer-Systeme leisten können

## **Ein elegantes Chaos**

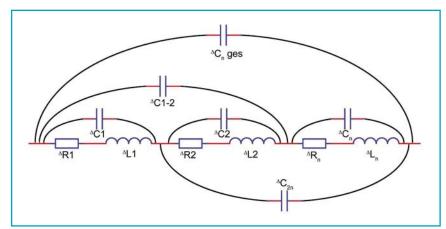

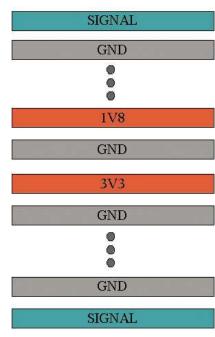

Der Aufbau des Multilayers bestimmt maßgeblich die Funktionen einer elektronischen Baugruppe. Um deren störsicheren Betrieb zu gewährleisten, müssen Stromversorgung, Signalintegrität und Impedanz des Multilayers kontrolliert werden. Alle drei physikalischen Eigenschaften lassen sich durch die strategische Anordnung der beiden elementaren Lagentypen Stromversorgungs- und Signalebene realisieren. Obwohl das "meltemi"-Board mit insgesamt 20 Lagen weit von einem Standardprodukt entfernt ist, lässt sich die der hier geschilderte Multilayer-Aufbau auch auf einen 10- oder 8-Lagen-Multilayer übertragen.

**Arnold Wiemers**

Auf einem Multilayer sind die elementaren Verbindungskomponenten für die Funktion einer elektronischen Baugruppe die Signalleiterbahn (Vcc) und die Stromversorgung (GND). Die Signalleiterbahn transportiert die Information, die zwischen den Bauteilen ausgetauscht wird. Die Stromversorgung liefert den Bauteilen die dazu notwendige Energie.

Die Signalleiterbahnen sind im Prinzip als Draht ausgelegt, der zwei oder mehrere Bauteilpins diskret miteinander verbindet.

Die Stromversorgungen sind flächig ausgelegt.

Es gibt zwei elementare Lagentypen: Die Signalebene und die Stromversorgungsebene.

Für den störsicheren Betrieb einer Baugruppe müssen (mindestens) drei Eigenschaften kontrolliert werden: die Stromversorgung,

die Signalintegrität und die Impedanz.

Diese drei Eigenschaften sind in einem Multilayer durch den Einsatz der o.a. elementaren Lagentypen modular verwirklicht:

Die Stromversorgung wird über Stromversorgungsebenen ermöglicht.

Die Signalintegrität setzt eine Signalebene voraus und benötigt eine Stromversorgungsebene für den rückfließenden Strom.

Die Impedanz setzt eine oder zwei Signalebenen voraus und benötigt eine oder zwei Stromversorgungsebenen als kapazitive Referenz. Es ist für jede dieser drei Eigenschaften typisch, dass nur eine, nur zwei oder nur wenige Ebenen eines Multilayers erforderlich sind. Daraus folgert, dass diese Eigenschaften modular in einem Teilkompartiment des Multilayers umsetzbar sein müssen.

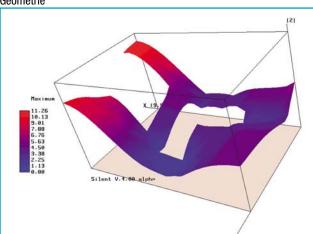

### Die Aufbaugeometrie von Multilayer-Systemen

Weiter ergibt sich, dass nur genügend Ebenen in einem Multilayer vorhanden sein müssen, damit Module mehrfach reproduziert werden können. Und weil nur die zwei elementaren Lagentypen der Signalebene und der Stromversorgungsebene benötigt werden, ist offensichtlich, dass es topologische Überdeckungen in der Aufbaugeometrie eines Multilayers geben muss.

■ Multi-Power-Systeme

Für die EMV-Stabilität einer Baugruppe ist es von großem Vorteil, wenn Störungen in der Stromversorgung entkoppelt und gepuffert werden. Dazu kann die Kapazität von Kondensatoren genutzt werden. Zwischen flächigen Stromversorgungsebenen unterschiedlicher Spannung ergibt sich jedoch auch eine Kapazität. Voraussetzung ist, dass die agierenden Flächen

## walter emmen

Geräte und komplette Einrichtungen für:

- ✓ Ein- u. doppelseitige Leiterplatten

- ✓ Durchkontaktierte Leiterplatten

- ✓ Multilayer

Ätzen, Entwickeln, Strippen

Kleingalvanikanlagen und Oberflächenfinish für Trommel- und Gestellware

- ✓ Vergolden, Versilbern

- ✓ Verzinnen, Verzinken

- √ Vernickeln, Verkupfern

- ✓ Entfetten

- √ Färben

- ✓ Eloxieren

Spülwasserreinigung und Filteranlagen

- ✓ Spülwasserreinigung

- ✓ Metallrückgewinnung

- ✓ Recyclingsysteme

- ✓ Filtration

Spülwasserreinigung / Metallrückgewinnung

Kleingeräteprogramm und Zubehör

- ✓ Tischgalvanisierwannen

- ✓ Trommeln

- ✓ Halterungen

- ✓ Anoden

Sonderanlagenbau

#### Walter Lemmen GmbH

Birkenstraße 13 D-97892 Kreuzwertheim

Tel. +49-(0)-9342 / 7851

Fax: +49-(0)-9342 / 2 11 56 E-Mail: info@walterlemmen.de

www.walterlemmen.de

Besuchen Sie uns:

M PRODUCTRONICA

räumlich benachbart sind und dass ihr Abstand zueinander hinreichend gering ist.

Bei der Konstruktion eines Multilayer-Systems ist also zu berücksichtigen, dass die Stromversorgungsebenen übereinander liegen.

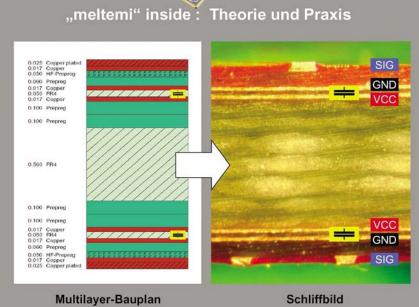

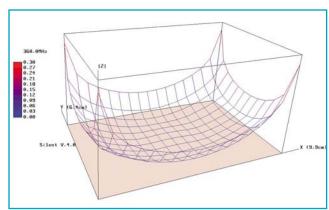

Damit genügend Kapazität aufgebaut werden kann, darf der Abstand der Stromversorgungsebenen nicht über 75 µm liegen. Ideal ist ein Lagenabstand von 50 μm.

Laminate und Prepregs mit einer Dicke von 50 µm sind heute standardseitig verfügbar.

Die Kapazität eines solchen Stromversorgungssystems ist proportional zur Fläche. Wird mehr Kapazität benötigt, als durch die Leiterplattengrundfläche zur Verfügung gestellt werden kann, dann kann die GND-Versorgung gedoppelt werden. Reicht das immer noch nicht aus, dann kann eine komplette weitere Vcc-Ebene plus einer GND-Ebene als Modul eingefügt werden.

Auf diese Weise entsteht eine gestapelte Stromversorgung in mehreren benachbarten Ebenen eines Multilayers und man spricht von einem Multi-Power-System (MPS).

Dabei kann es sich bei den hier pauschal als "Vcc" deklarierten Ebenen durchaus um unterschiedliche Spannungen handeln, wie das in der heutigen Praxis auch üblich ist.

Wichtig bei den Multi-Power-Systemen ist, dass der Stromversorgungsstapel oben und unten jeweils mit einer GND-Ebene abgeschlossen wird. Durch diese konstruktive Vorgehensweise wird die Schaltung vor den selbsterzeugten Störungen abgeschirmt, die sich auf den eigenen Vcc-Ebenen ergeben.

#### Impedanz der Signalleitung

Die Berücksichtigung der Impedanz einer Signalleitung sorgt für die kontrollierte Signalübertragung mit Blick auf die Signallaufzeit und den Leitungswiderstand.

Für die Realisierung der Impedanz werden eine oder zwei Signalebenen und eine oder zwei Stromversorgungsebenen benötigt. Innerhalb des Lagenaufbaus soll die Signalführung bei einem Lagenwechsel nicht zu einem Impedanzwechsel und möglichst auch nicht zu einem Wechsel der Leiterbahngeometrie führen.

Bestimmend für den Wert der Impedanz sind einerseits die Leiterbahnbreite (die hier im Zusammenhang mit dem mecha-

Für die EMV-Stabilität der Baugruppe ist es von Vorteil, wenn Störungen in der Stromversorgung entkoppelt und gepuffert werden

■ Die Berücksichtigung der Impedanz einer Signalleitung sorgt für die kontrollierte Signalübertragung im Hinblick auf die Signallaufzeit und den Leitungswiderstand

Für die hohe Integrität der Signale ist ein Übersprechen zwischen benachbarten Signalleitungen soweit wie möglich zu reduzieren

■ Die Konstruktion des Multilayer-Systems für das meltemi-Board

nischen Lagenaufbau ignoriert wird) und andererseits der Lagenabstand zwischen Signalebene und Stromversorgungs-

In den Lagenaufbau können berechnete und erprobte Impedanzmodule integriert werden. Diese Impedanzmodule sind innerhalb des Multilayeraufbaus anreihbar. Impedanzmodule, die eine Außenlage einbeziehen, können auf der gegenüberliegenden Außenlage spiegelsymmetrisch angefügt werden.

#### Signalintegrität

Der Rücklauf eines Signals erfordert eine GND-Ebene. Für die hohe Integrität der Signale ist ein Übersprechen zwischen benachbarten Signalleitungen soweit wie möglich zu reduzieren.

Bei höherlagigen Multilayern ist zudem zu beachten, dass der Abstand zwischen benachbarten Lagen geringer sein kann, als der Abstand zwischen Leiterbahnen in der gleichen Ebene.

Weil der Informationstransfer in einer Signalleitung in Form elektromagnetischer Felder stattfindet, ist eine hohe Signalintegrität an die räumliche Kontrolle dieser Felder gebunden und an die kontrollierte Rückführung des Signals über die GND-Ebene.

Diese Bedingung ist dann erfüllbar, wenn jeder Signalebene eine GND-Ebene zugeordnet ist. Damit die Lagenanzahl nicht übermäßig zunimmt, kann die Multilayer-Konstruktion so ausgeführt werden, dass zwei innen liegende Signallagen zwischen zwei GND-Ebenen liegen. Jede Signallage nimmt die jeweils näher gelegene GND-Ebene als Rücklaufebene an und baut nur einen geringen oder gar keinen störenden Bezug zur entfernter gelegenen GND-Ebene auf.

Aus dieser theoretischen Betrachtung ergibt sich allerdings auch bereits, dass maximal zwei Signallagen zwischen zwei

#### Gebt modernen Lösungen eine Chance

Oft unterliegen Ansätze für die technische Lösung einer Aufgabenstellung modischen Strömungen. Was nicht "en vogue" ist, wird übersehen oder ignoriert, auch wenn die Physik sich bereits zweifelsfrei entschieden hat.

Wahrscheinlich leben wir im Zeitalter der Elektronik. Mit Sicherheit leben wir in einem Zeitabschnitt, in dem eine Lösung sofort favorisiert wird, wenn sie Strom verbraucht. Den Widrigkeiten der EMV und der Signalintegrität stellt man elektronische Lösungen gegenüber. Überschüssige Energien auf Baugruppen werden verheizt oder erdrosselt. Dass es für viele Aufgabenstellungen einfache mechanische Lösungen geben könnte, scheint unvorstellbar zu sein. Erst recht, wenn sich das dunkle Geheimnis einer störungsfreien Baugruppenfunktion im Inneren eines Multilayers verbirgt. Und, noch schlimmer, wenn es kein Expertensystem und kein Tool dafür gibt. Für die Modernität und die Eleganz des Erfolges steht zur Zeit nur ein einziges archaisches Mittel zur Verfügung. Das eigenständige Nachdenken.

GND-Ebenen möglich sind. Bei drei oder mehr Signallagen wäre ein Übersprechen wegen der sich überlagernden Felder unumgänglich.

Bei außen liegenden Signalen ist nur eine Signalebene über einer GND-Ebene machbar. Grundsätzlich ist eine Belegung der Außenlagen eines Multilayers mit Signalebenen vorteilhaft. Umgekehrt ist aus kombinatorischen Gründen eine auf den Außenlagen liegende GND-Ebene nicht empfehlenswert.

#### ■ Kombination der Funktionsmodule

Die Lagenanzahl eines Multilayers kann und soll nicht beliebig zunehmen. Die Analyse der Funktionsmodule zeigt, dass die Anforderungen an die Impedanz und an die Signalintegrität von der Aufbaumechanik eines Multilayers her identisch sind.

Ein korrekt definiertes Impedanzmodul zeichnet sich deshalb auch immer durch eine hohe Signalintegrität aus. Das strategische Ziel bei der Konstruktion eines

Multilayersystems ist immer die gemeinsame Nutzung von Stromversorgungsebenen, insbesondere der GND-Ebenen. Bei Multi-Power-Systemen sind die äußeren GND-Ebenen gleichzeitig die Bezugsebenen für die Impedanz- und für die Signalintegritätsmodule.

#### ■ Fazit

Der Lagenaufbau der CPU meltemi ist mit insgesamt 20 Lagen sicherlich kein Standardprodukt. meltemi zeigt aber die kombinatorische Vielfalt der Anwendungsmöglichkeiten, die sich auch bei 10-Lagen- oder bei 8-Lagen-Multilayern umsetzen lassen. Maßgeblich ist, dass sich diese technischen Eigenschaften der Baugruppe durch die überlegte Konstruktion des Multilayersystems ergeben. Faktisch werden die physikalischen Eigenschaften durch die strategische Anordnung der Ebenen erreicht. Dass dafür zwei oder drei GND-Ebenen zusätzlich eingebaut werden müssen, kann akzeptiert werden. (cm)

#### Ihr preisbewusster Leiterplattenlieferant

Online Preise berechnen Online bestellen Online Aufträge verfolgen Online 24/24 Std. und 7/7 T.

Interessiert ? Sie erreichen uns unter: +49 2681 4662 E-mail: euro@eurocircuits.com

www.eurocircuits.com

- Pooling für Standard-Leiterplatten

- bis 6 Lagen

- von 1 bis 1000 Stück

- ab 3 Arbeitstagen

- Pooling mit Extra-Optionen

- bis 8 Lagen

- von 1 bis 1000 Stück

- ab 3 Arbeitstagen

- Ihre Platine-unsere Herausforderung

- bis 16 Lagen

- von 1 Stück bis ...

- ab 3 Arbeitstagen

#### Die Konsequenzen für Entflechten und Routing

## Nur ein Stück Draht

Eine Leiterbahn ist im Prinzip nichts anderes als ein Stück Draht. Dieses einfache Stück Draht hat die besondere Eigenschaft, Energie abzustrahlen, aber auch aufzunehmen. wenn es mit einer Wechselspannung beaufschlagt wird. Elektronikentwickler sind seit jeher gezwungen, diese Eigenheiten von einem Stück Draht zu berücksichtigen. Sei es gewollt zum Bau von Antennen oder um im Leiterplattenlayout ungewollte Abstrahlung auf einen akzeptablen Rest zu reduzieren. Die Hebel sind die Impedanz eines Stück Drahtes oder der Leiterbahn sowie die Geometrie der Verdrahtung bzw. das Entflechten und Routing der Leiterzüge.

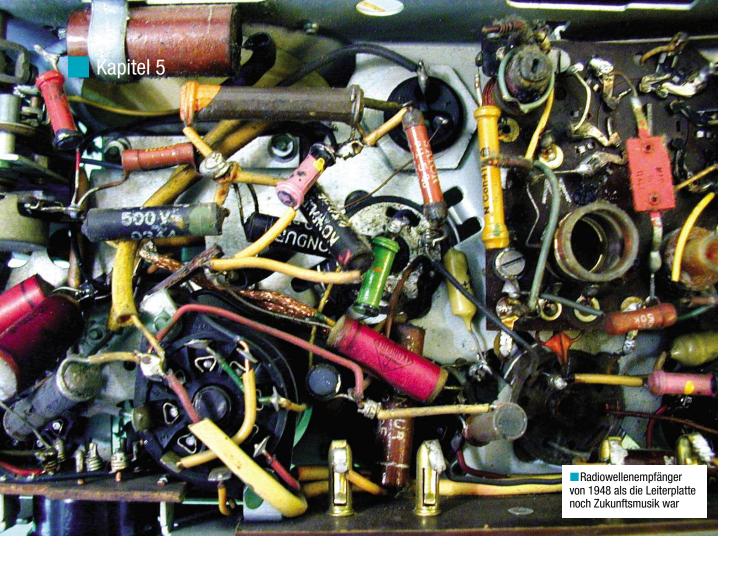

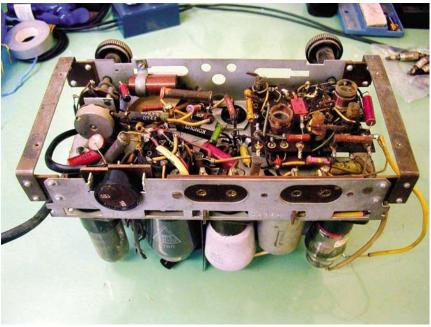

In den Anfangszeiten der Elektronik, als Röhren den Stand der Technik verkörperten, wurde vorzugsweise von "Hand" verdrahtet. Bild 1 zeigt einen Radiowellenempfänger für Lang- und Mittelwelle (ca. 300 kHz bis 1,5 MHz) in einem damals schon revolutionären Aufbau in dreidimensionaler Mehrlagenund Mehrebenen-Technik. Die Probleme mit dem Aufbau waren überschaubar, die Leiterplatten noch Zukunftsmusik. Angenehmes Arbeiten mit Sinussignalen stand im Vordergrund, Rechtecksignale blieben vornehmlich theoretischer Natur. Die wenigen "Oberwellen" wurden, falls vorhanden und unerwünscht, einfach weggefiltert. Platzprobleme gab es kaum und auch die EMV war ansonsten unbekannt und natürlich unbenannt. Dem steht, das in Bild 2 gezeigte Beispiel die "Leiterplatte 2010" als Baugruppenträ-

tigter 20-lagiger Multilayerprint mit hochintegrierten Bauelementen.

Was haben nun beide Module gemeinsam? Ist denn eine Gegenüberstellung nicht eher leichtsinnig und überhaupt sinnvoll?

Beide Aufbauten funktionieren einwandfrei – auch der Röhrenempfänger aus dem Jahr 1948!

Der "Draht" im alten Röhrenaufbau und die Verdrahtung auf und innerhalb des Multilayers scheinen sogar gleichen physikalischen Gesetzmäßigkeiten zu folgen.

### Was ein Radiowellenempfänger von 1948 und ein moderner Multilayer gemeinsam haben

Offensichtlich haben die damaligen Konstrukteure entweder "instinktiv" oder bewusst (wir werden der Frage noch auf den Grund gehen) eigentlich alles richtig gemacht. Der Mehrzahl heutiger zertifizierter "Amateurfunker" ist aus dem Antennenbau und aus der Kabeltechnik ein Begriff geläufig, der eigentlich jedem Techniker der Leiterplatten entflechtet, ebenso jedem Elektronikingenieur der Schaltungen entwirft, im Schlaf bewusst sein sollte: Die Impedanz eines mit Wechselspannung beaufschlagten Drahtes oder Leiterbahn!

Physikalische Gegebenheiten sind definitiv nicht verhandelbar! Dies sei ausdrücklich jenen Kaufleuten nahe gelegt, die auf Teufel komm raus nicht nur die Gesamtkosten eines Produkts reduzieren wollen und nach den Gesetzen der freien Marktwirtschaft auch müssen, sondern maßgeblichen Einfluss auf die technische Realisierung nehmen ohne die dazu notwendigen physikalischen Grundlagen verinnerlicht zu haben.

Die ungeliebte Leiterplatte steht besonders häufig im Fokus: "Da müssen doch zwei Lagen auch reichen oder noch besser nur eine"!

Das dicke Ende folgt spätestens in der EMV-Prüfhalle auf dem Fuße. Die Interpretation der zumeist katastrophalen Ergebnisse obliegt dann interessanterweise wieder ausschließlich der Kompetenz des Entwicklers, jedoch, wen wundert's, verbunden mit der Auflage das Problem wiederum "kostenneutral" zu lösen.

#### Die besondere Eigenschaft von einem Draht oder einer Leiterbahn bei Wechselspannung

Apropos Draht, respektive Leiterbahn: Wie kann man als Layouter einer Leiterplatte diesen Begriff visualisieren? Gleichspannungsmäßig ist darin eine leitende Verbindung zwischen A und B zu sehen, in der ein Strom (I) fließt die mit der Spannung (U) beaufschlagt ist. Bei einem gewünschten Strom (I) lässt sich der maximal vertretbare ohmsche Widerstand (R) abhängig von der Temperatur der Umgebung der Leiterbahn eindeutig durch die Breite, Dicke und Länge der Leiterbahn festlegen. Die maximal geforderte Spannung (U) bestimmt wiederum die Isolationseigenschaften und den geringsten Abstand der Leiterbahnen zueinander.

| Frequenz | Eindringtiefe |

|----------|---------------|

| 50 Hz    | 9,38 mm       |

| 10 kHz   | 660 μm        |

| 10 MHz   | 21 μm         |

| 1GHz     | 2 μm          |

Tabelle: Im Inneren einer Leiterbahn wird die Stromdichte mit steigender Frequenz kleiner als an der Oberfläche (Skineffekt)

## Funkentstörung und elektromagnetische Verträglichkeit

Zertifiziert nach DIN iSO 9001 durch

NKL GmbH Birkichstraße 15 74549 Wolpertshausen Tel. (0 79 04) 97 81-0 Fax (0 79 04) 97 81-50 E-Mail: info@nkl-emv.de Internet: www.nkl-emv.de

#### Produktion von:

- Entstördrosseln

- Entstörfilter

- Speicherdrosseln

- Metallpulverkernen

- Ringkernübertragern

- I/U-Wandler

#### Unsere Dienstleistungen:

- EMV-Messung

- Beratung und Schulung

- Funkentstörung

- Freifeldmessung

- Oberwellenmessung

- Flickermessung

■ Bild 1: Radiowellenempfänger in Röhrentechnik von Hand verdrahtet in damals revolutionärer dreidimensionaler Mehrlagen- und Mehrebenen-Technik

HF-Ingenieuren und besonders oben genannter seltener Spezies der Amateurfunker ist die Erkenntnis, dass ein Stück Draht beliebiger Länge im Vakuum gespannt einen Impedanzwert von annähernd

377  $\Omega$  [(120  $\cdot$   $\pi$ ) = Wellenwiderstand des Vakuums] annimmt, offensichtlich in die

annımmt, oπensichtlich in die "technische Wiege" gelegt.

Die Impedanz einer Dipolleitung beträgt unter entsprechenden Voraussetzungen 240  $\Omega$ , bei einem Stück Draht von ca. 16 m Länge in 10 m Höhe über dem Erdboden und einer bestimmten Frequenz exakt 50  $\Omega$ . Mit anderen Frequenzen lassen sich Bereiche von z.B. 140 bis 2000  $\Omega$  Impedanz überstreichen.

Die Vermutung, dass die Geometrie der Verdrahtung offenbar entscheidend für die Impedanz ist, wird zur Gewissheit. Diese Tatsache gilt in wesentlich kritischerem Maß für die Entflechtung und das Routing auf der Leiterplatte. Im Gegensatz zur "statischen" Gleichspannung bilden sich bei dynamischen Vorgängen elektrische UND magne-

tische Felder um eben dieses Stück

Draht oder Leiterbahn herum aus.

Heinrich Hertz, der damit auch die Funktechnik aus der Taufe hob, erkannte gegen Ende des 19. Jahrhunderts Folgenschweres: Diese Felder beeinflussten benachbarte Drähte und Leitungen dahingehend, dass offensichtlich ein Teil der Energie des "Sendedrahtes" auf parallel dazu liegenden Nachbarleitungen übertragen wurde.

Dem einfachen Stück Draht oder Leiterbahn muss also die besondere Eigenschaft zugestanden werden, Energie abzustrahlen, aber auch aufzunehmen. Also ein Sender-Empfängerprinzip! Daraus lassen sich unmittelbare Forderungen ableiten: a) Leitungen nicht über längere Strecken parallel führen (Vermeidung von Übersprechen). b) Signalleitungen UND deren Rückstromleitungen müssen möglichst nahe beieinander geführt werden. c) Jede Veränderung der Geometrie des Leiters ODER der Rückstromleitung ändert die Impedanz. Wird diese Tatsache ignoriert sind Signalintegritätsund EMV-Probleme unvermeidbar.

#### In der Praxis muss man Kompromisse machen

Die Praxis zeigt aber auch, dass Kompromisse gemacht werden müssen. Ein Beispiel soll das verdeutlichen: Ein Via ist üblicherweise 90° zu einer Leiterbahn angeordnet. Deswegen bringt die Polarisation

■ Bild 2: 20-lagiges meltemi-Board: Baugruppe für die serielle Hochgeschwindigkeits-Datenübertragung im Multi-Gigabit/s-Bereich

der Welle bei kreuzweiser (orthogonaler) Führung der unmittelbaren Nachbarleitung einen mehr als beachtlichen Faktor 100 in Bezug auf Übersprechen bzw. gegenseitiger Beeinflussung.

Kurz ein paar Worte zur Polarisation. Sie wird in der Fachliteratur meistens sehr kompliziert erklärt. Eine umfassende Definition derselben ist deshalb recht aufwändig.

Grundsätzlich versteht man unter der Polarisation die Lage elektrischer Feldkomponenten einer elektromagnetischen Welle in Bezug zu einem Rückleiter (meist Erdoberfläche in der Antennentechnik).

Die Lage der Welle (des Feldes) wird mit einem Richtungsvektor bezeichnet. Mittels der Vektoren (grafisch) kann man sofort durch Addition bzw. Subtraktion von Feldern, Wellen (bzw. deren graf. Vektoren) das Ausmaß bzw. die Wirksamkeit von Maßnahmen zur Unterdrückung von Feldern erfassen.

Fazit:

Damals wie heute sind Entwickler und Konstrukteure gezwungen, die erstaunlichen Eigenheiten eines Stück Drahtes unter Wechselspannungsbeaufschlagung zu berücksichtigen, sei es gewollt zum Bau von Antennen oder um im Leiterplattenlayout ungewollte Abstrahlung auf einen akzeptablen Rest zu reduzieren.

Hinzu kommt als Forderung in verstärktem Maße, dass bei den heute üblichen

Frequenzen und Schaltzeiten fast immer "vergessen" wird, die Eindringtiefe (Skineffekt) zu berücksichtigen. Im Inneren des Draht- oder Leiterbahnstücks wird die Stromdichte mit steigender Frequenz kleiner als an der Oberfläche (siehe Tabelle).

Folgende Faustformel lässt sich für den Bereich Leiterplatte (Material Cu,  $\varepsilon r = 4.3$ )

Ersatzbild eines Leiters: Ein Stück Draht beliebiger Länge hat im Vakuum einen Impedanzwert von annähernd 377  $\Omega$  $[(120 \cdot \pi) = \text{Wellenwiderstand des Vakuums}]$

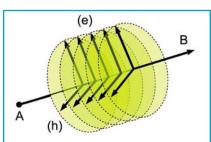

#### ◀ Bild 4:

Ausbreitung einer Welle: A – Ort der Aussendung, AB - Ausbreitungsrichtung, e = elektrisches Feld, h = magnetisches Feld

mit ausreichender Annäherung heran-

Eindringtiefe in Cu/mm =  $66.3/(\sqrt{(f[Hz])})$

Im Endeffekt zählt nur das Ergebnis: Sei es aus empirischer Erfahrung "herausdestilliert", mühsam mittels mathematischer Verfahren errechnet oder mittels teurer Softwarepakete erkauft.

#### Bild 5:

Beispiel einer Leiterbahnführung: Keine parallel geführten Strukturen auf der meltemi-Platine, vergleichbar mit dem handverdrahteten "multidimensionalen" Aufbau in Bild 1

#### Literatur:

Bild 1: Alfred Obermayer OE3AOW, Amateurfunker Frank Sichala, DL7VS, Die HB9CV Antenne Pierre Villemagne, Antennen für die unteren Bänder Rothammels Antennenbuch Hannu Tikkanen, Printed Circuit Board Design Guide RRL-Handbook 2005 (American Radio Relay League) Heiko Dudek, Cadence Designs Systems:

Differentielle Signalführung in PCBs

### alpha-board. Elektronik-Design und -Fertigungsservice

- Hardware-Entwicklung

- Leiterplattenentflechtung

- Board Simulation Signal- und Powerintegrität Leitungsanpassung Analyse des Übersprechverhaltens

- Thermische Simulation Bestückung

- Mechanisches Design

Qualitätssicherung

- Leiterplattenlieferung

PLC Management

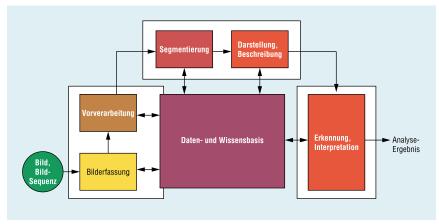

#### Signalqualität der Datenübertragungsleitungen analysieren

## In der EMV-Prüfhalle I

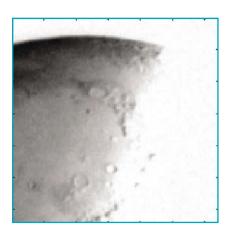

Signalintegrität schließt alle Probleme ein, die mit Leitungsverbindungen in der Hardware für Hochgeschwindigkeitsanwendungen auftreten. Mit ihren vielseitig programmierbaren I/O-Blöcken eignen sich FPGAs ideal zur Analyse der Signalqualität von Übertragungsleitungen auf der Leiterplatte und deren Verbindungen zu Steckerkonstrukten. Anhand von Messergebnissen untersuchen wir in diesem Kapitel die Signalqualität von Datenverbindungsleitungen zwischen SDRAM und FPGA des 20-lagigen "meltemi"-Boards.

Gerhard Eigelsreiter

Integrität: Ein Synonym für die kontinuierliche Übereinstimmung zwischen idealen und tatsächlichen in der Praxis auftretenden Werten, nicht in jedem kleinen Detail aber im Ganzen. Eine Umschreibung die, bezogen auf die Signalqualität, ein gehöriges Maß an freier Interpretation zulässt.

In der Elektronik schließt Signalintegrität im Allgemeinen alle Probleme ein, die mit (Leitungs-)Verbindungen in Hardwareprodukten für Hochgeschwindigkeitsanwendungen auftreten. Bei Übertragungsraten von 1 GBit/s und darüber ist es längst Usus geworden, Hardwareprodukte auf den Markt zu bringen, die so gerade noch in der EMV-Prüfhalle die Kurve kratzen.

Dabei gerät zwangsläufig die funktionale Stabilität unter die Räder, was sich im harmlosesten Fall besonders deutlich im Rückgang der tatsächlich übertragenen Nutzdaten niederschlägt.

Mit immer aufwändigeren Schaltungstricks und ressourcenfressenden mathematischen Algorithmen werden Fehlererkennung und -korrektur solange "fein-

getunt" bis sämtliche Mängel auf Kosten der Übertragungsrate der eigentlichen Daten eben mal soweit überdeckt sind, dass bei der Mehrzahl der Anwender und Benutzer der sprichwörtliche Geduldsfaden nicht sofort reißt, sondern aus Gewöhnungsgründen nur leicht überdehnt wird.

Dabei ließen sich die so gefundenen Lösungen wesentlich eleganter zur optimalen Ausnutzung vorhandener Kanalkapazitäten nutzen – funktional stabile und EMV-korrekt konstruierte Hardware vorausgesetzt.

#### Mit Messungen die Signalqualität untersuchen

FPGAs mit ihren vielseitig programmierbaren I/O-Blöcken eignen sich ideal zur Signalqualitätsanalyse von Übertragungsleitungen (z.B. Signalleitungen auf Leiterplatten) und deren Verbindungen zu Steckerkonstrukten, die zwangsläufig bereits in Hardware fixiert sind und oft schon als endgültige Board-Lösung vorliegen. Anhand von Messergebnissen soll

die Signalqualität von Datenverbindungsleitungen zwischen SDRAM und FPGA des 20-Lagen-meltemi-Boards näher untersucht und demonstriert werden.

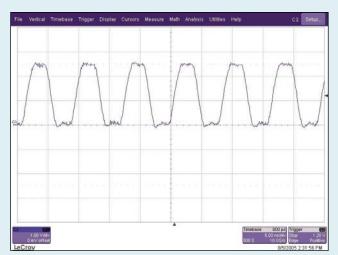

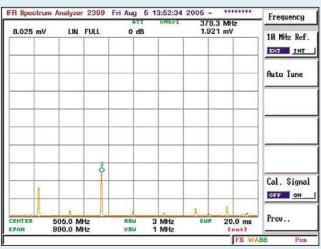

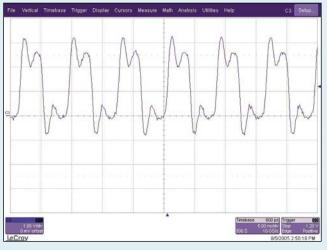

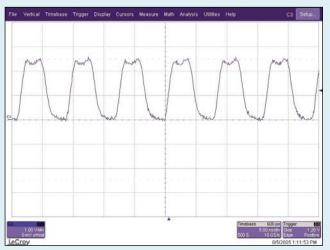

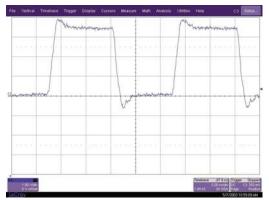

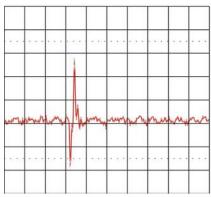

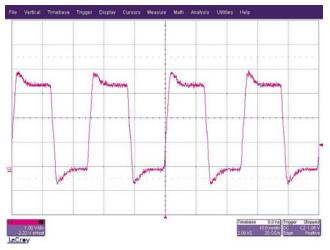

Zu diesem Zweck wurden die Datenleitungen DQ26 (Gesamtlänge 17 mm, nach 11 mm mit einem zusätzlichen Via zwecks Lagenwechsel) und DQ23 (Gesamtlänge 53 mm jedoch ohne Lagenwechsel, also kein Via) herangezogen. Beide Leitungen sind impedanzdefiniert (50  $\Omega$ ) ausgelegt und entsprechend geroutet. Bild 1 und 2 zeigen ein 125-MHz-Signal auf

der Datenleitung DQ26 bei einer Treibereinstellung des FPGA-I/O-Blocks im "12 mA Slow"-Mode. Dies entspricht ungefähr einer Treiberausgangsimpedanz von  $50\,\Omega$ . Wie nicht anders zu erwarten ein einwandfreies Signal. Dieselbe Leitung im "24 mA Fast"-Mode, Bild 3 (entspricht ungefähr  $20\,\Omega$  Treiberausgangsimpedanz).

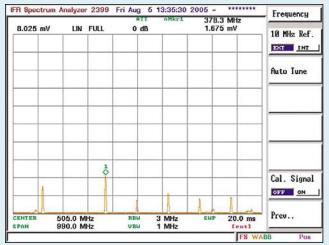

Aus Sicht der EMV mehr als bedenklich, siehe dazu Bild 4 Messung mit H-Feldsonde und Spektrumanalyzer. Die Resultate in der EMV-Prüfhalle bestätig-

Bild 1:

Die FPGA-Datenleitung DQ26 im 12-mA-Slow-Mode, 125 MHz, gute Signalqualität

Bild 2:

H-Feld-Sondenmessung von DQ26 am SDRAM-Eingangspin, 12-mA-Slow-Mode

#### Bild 3:

Die FPGA-Datenleitung DQ26 im 24-mA-Fast-Mode, Signalqualität im kritischen Bereich

#### Bild 4:

H-Feld-Sondenmessung von DQ26 am SDRAM-Eingangspin; 24-mA-Fast-Mode

■ Bild 5: Die FPGA-Datenleitung DQ26 im DCI-(Automatik)Mode, 125 MHz, gute Signalqualität

#### Bild 6:

H-Feld-Sondenmessung von DQ26 am SDRAM-Eingangspin, DCI-Mode

#### Die Hochgeschwindigkeitsplattform meltemi

Zentraler Dreh- und Angelpunkt des meltemi-Board ist ein FPGA mit integrierten seriellen Transceivern, umgeben von fest verdrahteter Unterstützungslogik und einem 32-Bit-Single-Chip-Mikrocontroller. Die mittels FPGA nach außen geführten Eingangs/Ausgangs-Ports sind in differenzieller Leitungstechnik ausgeführt. Von den insgesamt 77 differenziellen Kanälen sind 61 in LVDS-Technik mit einer Übertra-

gungsrate von 600 MBit/s/Kanal, also insgesamt mehr als 36 GBit/s brutto ausgestattet. Die restlichen 16 Kanäle werden von acht integrierten Transceivern mit 2,5 GBit/s/Kanal, insgesamt 40 GBit/s brutto, abgedeckt.

Vier Transceiver-Verbindungen laufen über jeweils zwei Infinibandund zwei Serial-ATA-Stecker-Komponenten nach außen. Die restlichen vier Transceiver als auch die insgesamt 61 LVDS-Leitungspaare benutzen vier impedanzdefinierte High-Speed-Buchsenleisten zwecks Erweiterung mit Aufsteckboards. Die zwei Infiniband-Steckverbinder sind nicht direkt an die Transceiver angebunden: Die sichere und problemlose Datenübertragung über längere Kabelverbindungen (bis 17 m) gewährleisten adaptive Kabel-Treiber und -Equalizer.

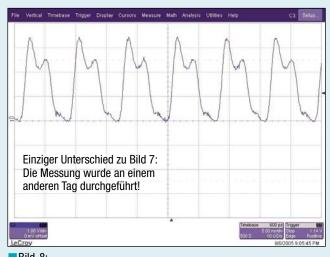

Bild 7: Die FPGA-Datenleitung DQ23 im DCI-Mode, 125 MHz, gute Signalqualität

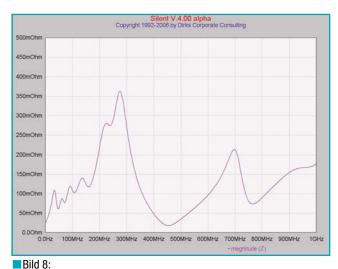

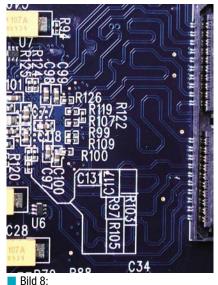

ten den ersten Eindruck. Man kann sich auch einer Automatik (DCI-Mode) bedienen, die über einen Referenzwiderstand  $(49,9 \Omega)$  die Ausgangstreiberimpedanz hinsichtlich Temperaturund Spannungsschwankungen laufend "nachzieht" – siehe Bild 5 und Bild 6. Diese elegante Lösung fand für die nächsten Messungen auf der Datenleitung DQ23 großen Anklang (Bild 7). Die Wiederholung der Messungen unter gleichen Messbedingungen am nächsten Tag löste allerding erhebliches Erstaunen aus - siehe Bild 8.

Die FPGA-Datenleitung DQ23 im DCI-Mode, 125 MHz, Signalqualität im kritischen Bereich

Tags darauf keimte bei der dritten Messserie mit wieder identischen Werten zu Bild 7 gewaltiges Misstrauen auf. Solche Differenzen sind selbst bei großzügigster Auslegung nicht mehr Messungenauigkeiten zuzuschreiben. Noch dazu tagesabhängig! Ein Zustand, der keinesfalls hingenommen werden konnte. Des Rätsels Lösung, mit schwerwiegenden künftigen Folgen aus Sicht der EMV und damit verbundener funktionaler Instabilitäten, steht im nächsten Kapitel. (cm)

#### HEGER GMBH Leiterplatten-Schnellservice

Leiterplatte in 4 Stunden  $\cdot$  Multilayer in 24 Stunden  $\cdot$  Garantierte Termintreue Entwicklung und Layout · Sonderleiterplatten · Bestückung und Test Mikroviatechnik · Mikrofeinstleiter · Mikro-BGA-LP's

www.hegerambh.com

Oststraße 83  $\cdot$  22844 Norderstedt  $\cdot$  Tel. 040/5225022  $\cdot$  Fax 040/5264554  $\cdot$  E-Mail: Leiterplatte@hegergmbh.com

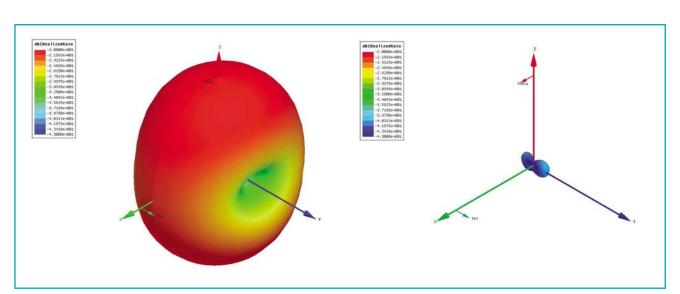

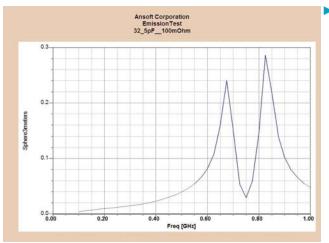

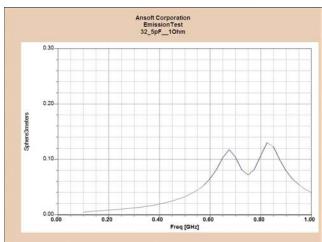

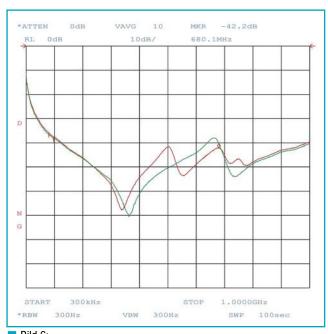

#### Einfluss von FPGAs auf das Abstrahlverhalten der Baugruppe

## In der EMV-Prüfhalle II

Die in Kapitel 6 beschriebenen tagesabhängigen Ergebnisse der Signalintegritätsmessungen trotz identischen Messaufbaus und identischer IOB-Einstellungen im FPGA haben bei den Entwicklern der Hochgeschwindigkeitsplattform meltemi intensive Nachforschungen ausgelöst. Schließlich kristallisierte sich in der Fehleranalyse der feine, aber entscheidende Unterschied heraus: Die aufgespielte FPGA-Software war für das Bestehen bzw. Nichtbestehen der EMV-Prüfung der Baugruppe verantwortlich.

Gerhard Eigelsreiter

Einer Legende nach entstand der Terminus "Bug" in der Anfangszeit elektronischer Rechenanlagen, als Insekten die Funktionsweise von Relais in großen Maschinen beeinträchtigten und sogar Kurzschlüsse verursachten. Auch für das Rauschen und Knistern in Telefonleitungen seien kleine Tiere verantwortlich, die ständig an den Leitungen knabbern. Eine Fehlfunktion wegen einer Motte im Relais des Computers Mark II Aiken Relay Calculator soll im Jahre 1945 die Computerpionierin Grace Hopper zu folgendem Eintrag veranlasst haben: First actual case of bug being found. Motte und Logbuchseite befinden sich derzeit am Smithsonian Institut.

Wie es sich für Insekten gehört, haben sich diese Bugs inzwischen rasend ver-

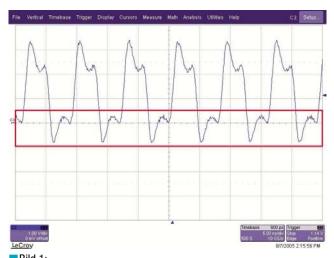

Die FPGA-Datenleitung DQ23 im 24-mA-Fast-Mode 125 MHz; untere Signalhälfte (hervorgehoben im roten Kasten) – Signalqualität im kritischen Bereich

mehrt und treten vorzugsweise in großen Schwärmen auf. Die Bekämpfung derselben erfolgt deswegen flächendeckend mit so genannten "Service-Paks". Inzwischen breiten sich die Bugs weiter in Richtung Signalintegrität und EMV aus, vornehmlich mittels reprogrammierbarer Logik.

#### Ursache für "tagesabhängige" Messergebnisse im EMV-Labor

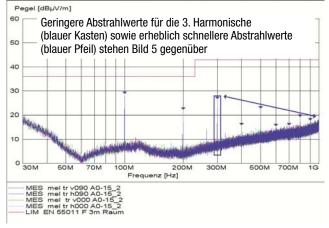

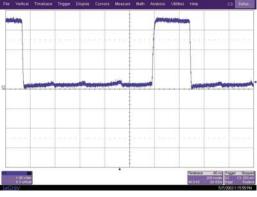

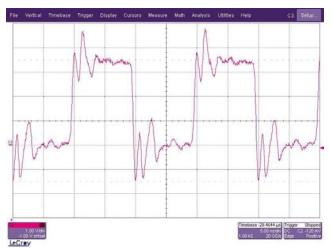

Tagesabhängige Ergebnisse, wie im Kapitel 6 beschrieben, lösen bei Signalintegritätsmessungen nahezu automatisch intensive Nachforschungen aus. Der direkte Vergleich der Messungen an der Datenleitung DQ23 (Eingangspin SDRAM) im 24-mA-Fast-Mode (Bild 1) zum DCI-Automatik-Mode (Bild 2) zeigte in den oberen Bildhälften (blauer und roter Kasten) verblüffende Übereinstimmungen. Eine höhere Auflösung der

Die FPGA-Datenleitung DQ23 im DCI-(Automatik-)Mode 125 MHz; obere Signalhälfte (roter Kasten) Signalqualität im kritischen Bereich; untere Signalhälfte (blauer Kasten) gute Signalqualität

Messung im Zeitbereich verdeutlicht die Problematik. Vergleicht man die Anstiegswinkel der Kurven beider Messungen beim Wechsel von Low auf High (Bild 3 und Bild 4), so erkennt man kaum einen Unterschied in der Anstiegszeit (blauer Kasten).

Dies ist umso bemerkenswerter, als es der per Software indirekt über den Treiberstrom einstellbaren, kürzest möglichen Flankenanstiegszeit entspricht. Hingegen weisen die fallenden Flanken, also der Wechsel von High auf Low, hinsichtlich der Abfallzeiten (roter Kasten) erhebliche Unterschiede auf. Die Anstiegszeit (blauer Kasten) des Signals im DCI-Automatik-Mode von Bild 4 entspricht also ziemlich exakt dem 24-mA-Fast-Mode, während die Abfallzeit (roter Kasten) dem gewünschten DCI-Automatik-Mode bei korrektem Betrieb gleicht. Wie ist so etwas möglich? Kann man Anstiegs- und Abfallzeiten getrennt programmieren? Ist derartiges überhaupt sinnvoll?

Natürlich nicht! Das gilt gleich als Antwort auf die letzten beiden Fragen.

Die Erklärung, wie so etwas überhaupt möglich ist, lässt sich nur mutmaßen. Trotz identischen Messaufbaus und identischer IOB-Einstellungen im FPGA kristallisierte sich doch ein feiner, aber letztendlich entscheidender Unterschied heraus. Der Schaltplan für diese Teststellung wurde mit Logiksymbolen erstellt, die aber bereits die grafische Darstellung hinterlegten VHDL-Codes repräsentieren.

Die Übersetzung des VHDL-Codes bis zur Erstellung des gewünschten Lade-Bitstroms dauerte zuweilen bis zu 10 Minuten (ist natürlich stark von der Performance des benutzten PCs abhängig). Da hier Messreihen mit hunderten von Messungen auf ihre Abarbeitung warteten, wurde eine Softwareabkürzung in Form des FPGA-Editor-Moduls benutzt. Eine Verkürzung der Zeitdauer zur Erstellung des Bitstromes auf unter zwei Minuten war der Lohn der Bemühungen, aber gleichzeitig auch die Lösung dieses Phänomens. Mittels des FPGA-Editors ist man in der Lage, die Attribute in den IOBs direkt zu setzen, vergleichbar mit einem Hex-Editor in der Software. Nach zwei Tagen Nachforschungen ließ sich der Unterschied in den Kurven reproduzierbar gezielt erzeugen. Jedes Mal wenn die Übersetzung per VHDL-Compiler sowie der entsprechenden Map-and-Place-Software den gewünschten Lade-Bitstrom erzeugte, trat die unerwünschte Differenz in den Anstiegs- und Abfallzeiten auf. Immer dann, wenn der FPGA-Editor zum Zuge kam, war das Ergebnis korrekt und die Anstiegs- und Abfallzeiten moderat, entsprechend den DCI-Mode-Vorgaben.

#### Unterschiedliche Ergebnisse durch Softwarebugs der FPGAs

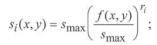

Also vermutlicher Weise wieder einmal eine zusätzliche Gattung dieser praktisch unvermeidbaren Softwarebugs mehr, an die man sich leidlich gewöhnt hat. Ein Schulterzucken, was soll's, auf zum nächsten Service-Pak. Tatsächlich nur ein unbedeutendes Ärgernis? Ein Blick in die EMV-Prüfhalle belehrt eines Besseren.

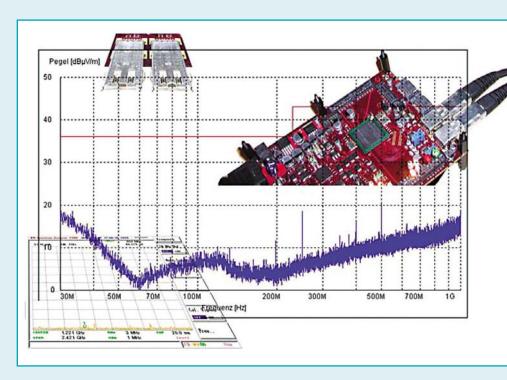

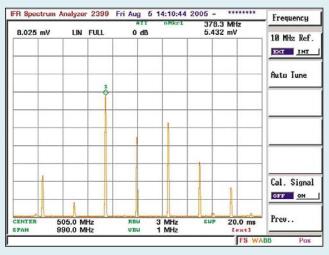

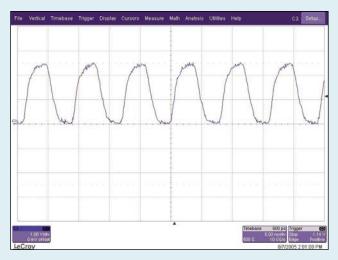

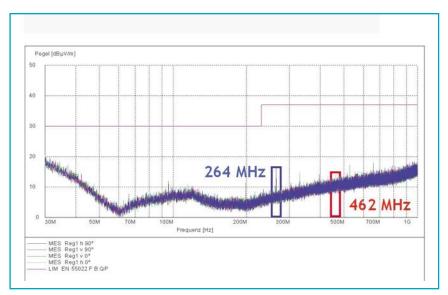

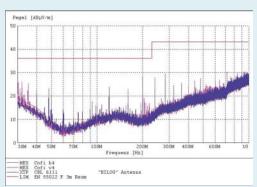

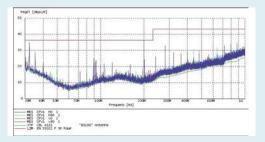

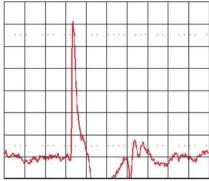

Zwecks übersichtlicherer Darstellung wurden gleich 16 Datenleitungen (DQ16 – DQ31) parallel mit 100 MHz betrieben und in

FPGA-Datenleitung DQ23 im 24-mA-Fast-Mode mit 1 ns/Teilung, also höher aufgelöst. Die Anstiegszeiten (blau) und die Abfallzeiten (rot) sind nahezu identisch.

Die FPGA-Datenleitung DQ23 im DCI-(Automatik-)Mode mit 1 ns/Teilung, ebenso höher aufgelöst. Die Anstiegszeiten (blau) und Abfallzeiten (rot) unterscheiden sich erheblich.

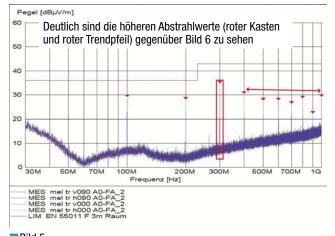

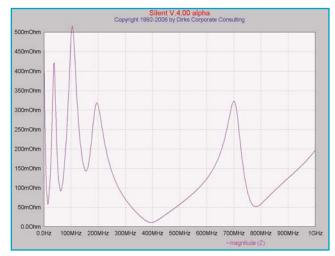

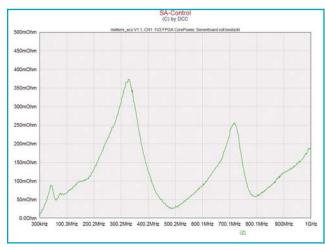

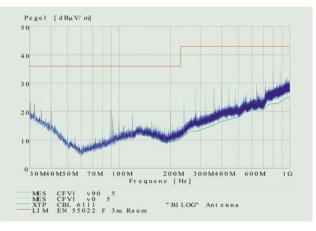

Störspektrum der meltemi-Baugruppe aus der EMV-Prüfhalle: 16 Datenleitungen (DQ16 bis DQ31) 24-mA-Fast-Mode

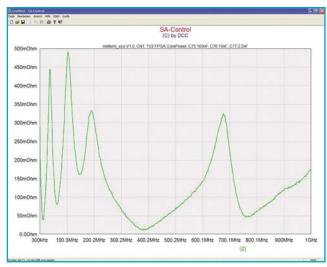

■Bild 6: Störspektrum der meltemi-Baugruppe aus der EMV-Prüfhalle: 16 Datenleitungen (DQ16 bis DQ31), DCI-(Automatik-)Mode im korrekten Betrieb

#### Die Tücken der FPGAs

Die Messgerätehersteller können sich die Hände reiben. Der Verzicht auf entsprechende Signalqualitätsmessungen vor der EMV-Prüfung kann leicht zum Überschreiten der Grenzwerte führen. Und das in einem Ausmaß, das eine positive Beurteilung der EMV-Prüfergebnisse nicht mehr zulässt.

In Zukunft auf reprogrammierbare Logik zu verzichten kann sicher nicht der Weisheit letzter Schluss sein, denn eine wachsende Zahl von Halbleiterherstellern gedenkt in den nächsten Jahren Mikrocontroller mit integrierter reprogrammierbare Logik auszustatten. Da wäre bestenfalls eine kurze Schonfrist herauszuholen, mehr nicht. Andernfalls darauf zu hoffen, durch Software-Updates das Problem in den Griff zu kriegen ist, könnte sich als trügerisch erweisen.