## **Die Leiterplatte 2010**

#### Kathrin Fechner **Arnold Wiemers**

## Die Leiterplatte 2010

Gestern...Heute...Morgen

#### Wie alles angefangen hat...

Aus meiner Sicht beginnt alles damit, daß Herr Eigelsreiter von der Fa. UNITEL mich bei ILFA anruft. Das ist gegen Ende 2002.

Er benötigt eine Leiterplatte für ein High-Speed-CPU-Board mit dem Namen "CERO". Das ist so oder ähnlich ein übliches Gespräch für einen Leiterplattenhersteller. So fängt es eigentlich immer an.

Allerdings soll "CERO" einen stabilen Datentransfer bis 10MBit/s leisten.

Der Informationstransport soll via LVDS erfolgen. Aufgabe ist zudem, ein Maximum an EMV-Stabilität und an Signalintegrität auf der Basis eines MultiPowerSystems zu erreichen. Das alles mit *normalen* Basismaterialien und mit den für die Produktion von Leiterplatten üblichen Herstellungsverfahren.

#### ...und warum das schon schwierig war...

Der Diskussionspartner für Herrn Eigelsreiter, die physikalischen Eigenschaften von "CERO" betreffend, ist Herr Prof. Dirks.

Die Leiterplatten für "CERO" werden von ILFA gefertigt. Besondere Merkmale sind der Aufbau des Multilayers und die Details der Fertigungstechnologie.

Signifikant sind ein 7-lagiges Stromversorgungssystem mit 50µm Abstand zwischen den Lagen, das Pluggen der Vias für das FPGA und die Metallisierung der Leiterplattenkanten.

Die Baugruppen für "CERO" werden in Berlin von der Fa. TAUBE ELECTRONIC bestückt.

"CERO" besteht auf Anhieb alle Tests im EMV-Labor im TGM in Wien mit Bravour.

#### ...und was dann kam...

"CERO" wird detailliert in der Elektronik Praxis in einer mehrteiligen Serie beschrieben. Die Veröffentlichung wird redaktionell von Frau Claudia Mallok begleitet.

"CERO" trifft mitten ins Herz der Entwickler von elektronischen Baugruppen und wird bereits im Jahr 2003 "Die Leiterplatte des Jahres 2005". Im Herbst erscheint zur Messe "Productronica" ein kompaktes Sonderheft in deutscher und englischer Sprache.

Die Leiterplattentechnologie und vor allem das physikalische Umfeld der Leiterplatten und Baugruppen wird komplexer. Deshalb gründet ILFA im gleichen Herbst die "ILFA-Akademie".

Der erste aller Fachvorträge wird :

"CERO: Aspekte einer High-Speed-CPU"

#### ...und wie es weiterging...

Monatelang passiert dann nichts mehr.

Herr Eigelsreiter ist als Referent gefragt. Er verlegt sich teilweise aufs Philosophische und prägt als Untertitel zum Seminar "CERO" den gleichrangigen 2. Titel:

#### ... Die Physik als Partner.

Das ist der richtige Denkansatz. In der Leiterplattentechnik werden Lagenaufbauten mit

impedanzdefinierter Signalführung en vogue.

Signalintegrität ist das Wort der Zeit.

Schaltungskonzepte werden komplex.

Auslöser dieser Entwicklung ist die Forderung

nach dem zuverlässigen Transfer sehr hoher

Datenvolumina. Die Leistung der elektronischen

Komponenten nimmt drastisch zu.

Systematische Konzepte fehlen aber noch.

#### ...um warum es noch schwieriger wurde...

Das Jahr 2004 beginnt zuerst sehr ruhig.

Herr Eigelsreiter überrascht mich im Frühjahr mit der neuen Erkenntnis, daß "Eine einfachere Einfachheit nur möglich ist vor dem Hintergrund einer komplexeren Komplexität".

Sein neues High-Speed-CPU-Board trägt den Namen "meltemi".

Die neue Baugruppe besitzt im Kern die erfolgreichen Konstruktionsprinzipien seines noch jungen Vorgängers.

Die dreidimensionale Geometrie der Leiterplatte wird systematisch verplant.

Es werden Funktionsräume geschaffen, um die unterschiedlichen elektrophysikalischen Anforderungen an die Leiterplatte zu lösen. Dazu muß ein 20-Lagen-Multilayer berechnet werden.

Signalintegrität Impedanz Modul

Multi-Power-System

Signalintegrität

Impedanz Modul

Signalintegrität

Signalintegrität

Impedanz Modul

Signalintegrität Impedanz Modul

#### ...und wie dann "Die Leiterplatte 2010" entstand...

"meltemi" funktioniert und wird mit allen Details in der Elektronik-Praxis veröffentlicht.

Um der futuristischen Perspektive genüge zu tun, wird auch "meltemi" umbenannt und bekommt den visionären und inzwischen allseits bekannten Namen "Die Leiterplatte 2010".

Es entstehen 14 Fachartikel, die in 2006 über viele Monate verteilt in der ElektronikPraxis publiziert werden.

Für die Leiterplatten Akademie GmbH baut Herr Eigelsreiter das Seminar "LP2010" auf.

Weil es heißt: "....mit 20 Lagen kann ich das auch" wird eine 6-Lagen-Variante gebaut mit dem passenden Namen "meltemi economic", die ebenfalls erfolgreich ist.

Im April 2007 erscheint das zweisprachige Blog Sonderheft "Die Leiterplatte 2010".

Die Aufmerksamkeit, die der Baugruppe zu teil wird, veranlaßt den FED bereits 2006, zummers Thema "High-Speed-Design" auf seiner Jahres konferenz in Kassel eine Podiumsdiskussion reiter anzubieten. Die Wogen schlagen hoch. Die Diskussion ist zwiespältig. Die physikalischen Hintergründe, die den Erfolg **3XIS** der Baugruppe "meltemi" ausmachen, werden nicht zweifelsfrei akzeptiert.

Die technische Funktion des Multilayers wird e 2010" nicht zweifelsfrei akzeptiert. Die problemlose Umsetzbarkeit der meltemi-Anforderungen auf einem CAD-System wird ohne zwingendes Ergebnis diskutiert. Podiumsdiskussion zur

Noch am gleichen Abend gründen Frau Mallok, Z 2006 Herr Eigelsreiter und Herr Wiemers deshalb die

"Projektgruppe 2010".

D-Konferenz 2006 Elektronik Praxis "Die Leiterplatte 2010"

#### ...und wie sich dieses Projekt entwickelte...

In Kassel werden grundlegende Fragen angesprochen aber nicht befriedigend beantwortet.

Das Projekt "Die Leiterplatte 2010" soll die P2010" Lücken verbindlich schließen. Die Gründungsveranstaltung ist Anfang Juli 2007 in München.

Als weitere Partner werden gewonnen:

Frau Jennifer Vincenz TILFA CAD

Herr Thomas Fend IDS

Herr Roland Krammer UNITEL

Herr RainerTaube TAUBE ELECTRONIC

Herr Ronald Weber DesConTec

Herr Gerd Prillwitz Ans

Frau Kathrin Fechner Leiterplatten Ak

Herr Dr. H. Poschmann FED

Ansoft LeiterplattenAkademie

Herr Eigelsreiter ist der verantwortliche Technologe. Frau Mallok und Herr Wiemers dürfen das Projekt leiten. Die Leiterplatte 2010 – ein zukunftweisend

#### ...und wie lange es dann doch noch dauerte...

Auf der FED-Konferenz im Herbst 2007 wird das Projekt der Öffentlichkeit vorgestellt.

Anfang 2008 sind die Schaltpläne, Stücklisten und Bauteilspezifikationen überprüft und an die Layouter/innen verteilt.

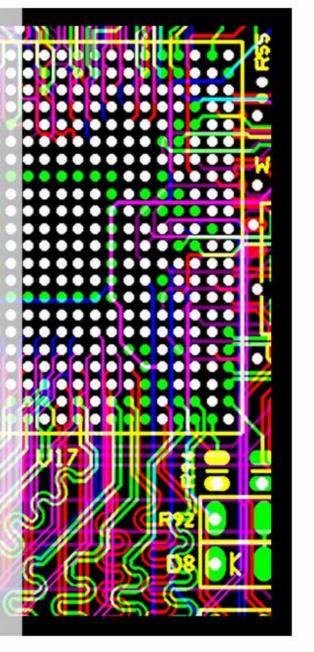

Wenn es die Zeit zwischendurch zuläßt, dann wird an den Layouts gearbeitet. Es entstehen unabhängig voneinander drei CAD-Layouts.

Es arbeiten daran :

Frau Lange TAUBE ELECTRONIC

Frau Vincenz ILFA CAD

Herr Wrchotka DesConTec (heute FlowCAD)

Zum Herbst 2009 sind die ersten Layouts fertig und werden traditionell auf der Jahreskonferenz des FED in Bamberg veröffentlicht.

#### ...und wie dann Baugruppen gebaut und geprüft wurden...

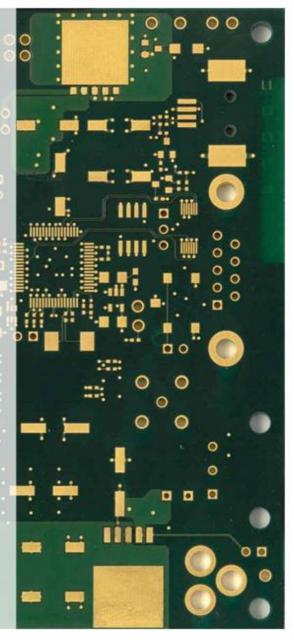

ILFA fertigt gegen Ende 2008 die Leiterplatten für dieses Projekt.

Die wirtschaftliche Gesamtsituation führt dazu, daß alles langsamer läuft. Für mehr als ein halbes Jahr gibt es keinen Fortschritt.

Insgesamt sind 100 Baugruppen vorgesehen, davon 45 für den ersten Abschnitt. Die Anzahl muß auf 15 Baugruppen reduziert werden.

Frau Mallok sucht und findet Unterstützung bei mehreren Bauteil-Distributoren. Frau Lange durchforstet und bereinigt die Stücklisten.

Anfang August 2009 beginnt die Fa. TAUBE ELECTRONIC mit der Bestückung.

Anfang September 2009 nimmt Herr Eigelsreiter die ersten Baugruppen in Graz in Betrieb und führt die entscheidenden Tests im EMV-Labor durch. Alle sind gespannt auf die Ergebnisse.

#### ...und daß das dann in keine Zeitung mehr paßte...

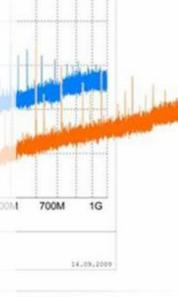

Die unter Zeitdruck in Betrieb genommenen Baugruppen bestehen den EMV-Test im ersten Anlauf.

Die schon obligatorische Veröffentlichung für die FED-Konferenz in Magdeburg wird erstellt. Inzwischen haben die erarbeiteten Ergebnisse ein erhebliches Volumen. Die Erkenntnisse aus der Layoutarbeit und aus der Produktion der Baugruppen sind ein dickes Kapitel geworden. Die Erkenntnisse aus dem EMV-Labor haben zu einem Stapel Meßkurven geführt, der analysiert und interpretiert werden will.

Das paßt auch dicht gedrängt nicht mehr in eine Fachzeitschrift. Es sind persönliche Gespräche erforderlich. Deshalb entscheidet die Gruppe, eine Fachtagung zur LP2010 zu organisieren.

#### ...und daß wir deshalb jetzt heute alle hier sind....

Als Termin für diese Fachtagung haben wir Donnerstag, den 18. März 2010 gewählt.

Das ist heute.

Wir sind hier.

Wir haben ein ausgezeichnetes Programm vor uns mit ausgezeichneten Vorträgen.

Sie sind hier.

Damit haben wir außerdem auch noch die besten aller möglichen Gäste.

Das "Gestern" und das "Heute" ist somit geklärt.

Doch was erwartet uns morgen?

#### ...und uns für morgen keine Sorgen machen müssen.

Wenn dieser Tag vorbei ist, dann wird die "Leiterplatte 2010" Spuren hinterlassen haben.

Was wir heute lernen, das haben wir gestern erarbeitet. Morgen wird uns das weiterbringen.

Vieles ist wichtig.

Wirklich unverzichtbar ist nur die partnerschaftliche Zusammenarbeit.

#### Vielen Dank an alle Partner/innen in diesem Projekt:

Ansoft (Gerd Prillwitz) / DesConTec (jetzt FlowCAD) (Ronald Weber, Martin Wrchotka) / Dirks Compliance Consulting (Nils Dirks) / ElektronikPraxis (Claudia Mallok) / Fa. Farnell / FED (Dr. Hartmut Poschmann, Michael Ihnenfeld) / IDS (Thomas Fend) / ILFA (Jennifer Vincenz, Arnold Wiemers) / Fa. Jauch / LeiterplattenAkademie (Kathrin Fechner) / Fa. Maxim / PhotoCAD (Herr Jepsen) / POLAR Instruments (Hermann Reischer) / Fa. Silica / Fa. Samtec / TAUBE ELECTRONIC (Angela Lange, Jürgen Paape, Rainer Taube) / Technolam (Volker Klafki) / tecnotron (Achim Schulte) / Unitel (Gerhard Eigelsreiter, Roland Krammer)

### Danke.

# Die Leiterplatte 2010

#### Kontakt LeiterplattenAkademie

LA - LeiterplattenAkademie GmbH Krefelder Straße 18 10555 Berlin

Geschäftsleitung: Kathrin Fechner

Telefon 030 / 34 35 18 99

Telefax 030 / 34 35 19 02

eMail info@leiterplattenakademie.de

Internet www.leiterplattenakademie.de