|

Seminar Leiterplatten 3 ...HighSpeedLeiterplatten

Technisch-physikalische Eigenschaften von Multilayersystemen mit hohen Ansprüchen an eine zuverlässige Signal- und Powerintegrität

|

Anforderungen an Leiterplatten

Technische Anforderungen für das CAD-Design elektronischer Geräte (SI, EMI, PI, MPS, Wärme). Anforderungen an die Qualität von CAD-Designs.

Allgemeine Eigenschaften von Leiterplattenklassen.

|

Leiterbildstrukturen

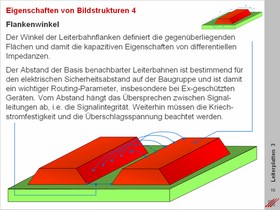

Elementare technische und physikalische Eigenschaften von Leiter-bildstrukturen. Lötfläche, Impedanz

und Entwärmung. Der Einfluß der Geometrien von Leiterbahnen auf die Funktion der Leiterplatte und des elektronischen Gerätes. Rückätzung und Ätzflanken.

|

|

|

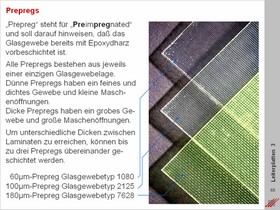

Basismaterial

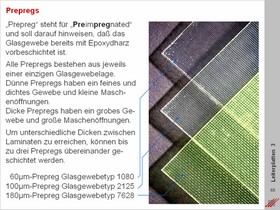

Basismaterialien für elektronische Geräte. Laminate und Prepregs.

Eigenschaften von Glasgeweben und Harzen. Übliche Werte für Kupferdicken. Diverse technische Werte, z.B. der Tg-Wert sowie die dieelektrischen Parameter, die Verlustwerte und der CTE-Wert.

|

Prepregs + Laminate

Der Einfluß diverser elementarer Materialeigenschaften auf die Qualität einer Übertragungsleitung.

Die Struktur von Glasgewebe und Glasgewebefäden. CAF.

Allgemeine Regeln für die Konstruktion von Multilayersystemen mit Prepregs unterschiedlicher Dicke.

|

|

|

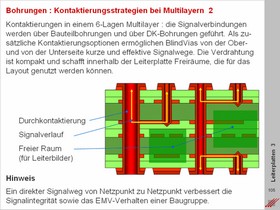

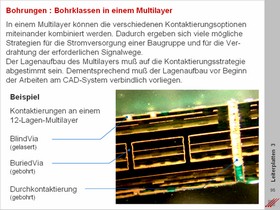

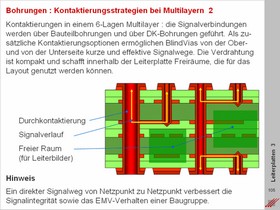

Kontaktierungsstrategien

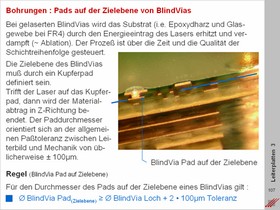

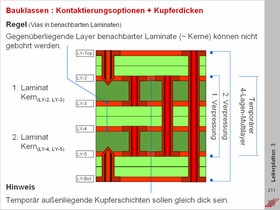

Kontaktierte und nichtkontaktierte Bohrungen.

Definition des Aspect Ratio für die Berechnung des Durchmessers und der kontaktierbaren Hülsenlänge für BuriedVias, BlindVias und THTs. Maximale Abstände zwischen den Lagen eines Multilayers.

|

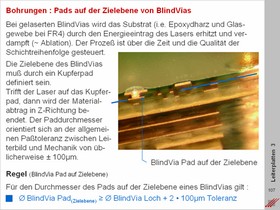

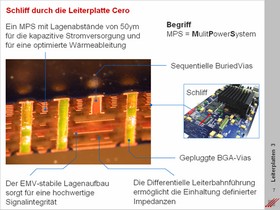

Vias

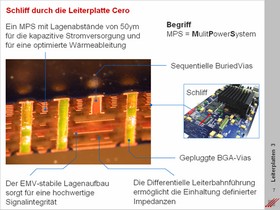

VIPs: CAD-Designs mit Vias in Pads ermöglichen eine hochdichte Entflechtung von Leiterplatten.

Mit Blick auf die Signalintegrität ist es möglich, Signalverbindungen kompakt und direkt zu verdrahten.

Die Konstruktion von Multilayern mit sequentiellen Kontaktierungen.

|

|

|

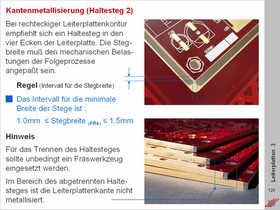

Metallisieren

Galvanische Produktionsprozesse für die Metallisierung von Bohrungen und Oberflächen.

Werte für diverse Kupferdicken.

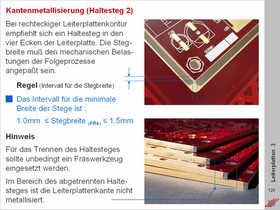

Die Kantenmetallisierung ermöglicht die Abschirmung der inneren Lagen eines Multilayers und verbessert das EMV-Verhalten.

|

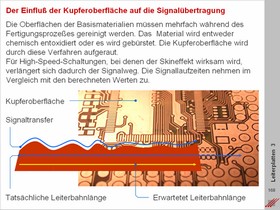

Endoberfläche

Der Einfluß der Oberfächenrauhigkeit auf die Signallaufzeit.

Gründe für eine plane und mikrorauhe Oberfläche.

Produktionstechnik und Konstruktion eines Multilayers für eine zuverlässige Signalübertragung.

|

|

|

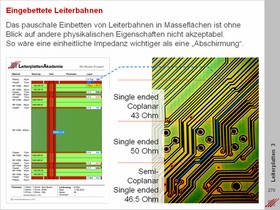

Routing

Elementare Regeln für das Routen von Signalleiterbahnen.Übliche Fehler beim Routing und bei der Einbettung von Leiterbahnen in Kupferflächen. Folgen des unkontrollierten Flächenfüllens.

Der Einfluß von Strukturabständen auf die Signalqualität.

|

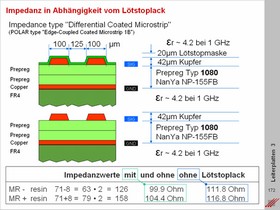

Lötsop- und Bestückungsdruck

2-Komponenten-Epoxydharzsyste-me und ihr Einflluß auf das physikalische Verhalten von Leiterbahnen für die Signalübertragung.

Dielektrika der Epoxydharze für Lötstoplack und Bestückungsdruck.

Veränderungen des Impedanz-wertes durch Lacke.

|

|

|

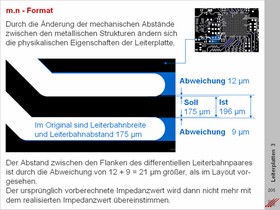

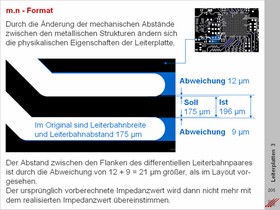

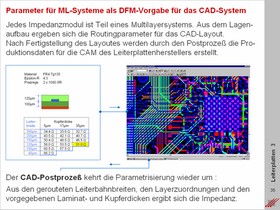

Datatransfer

Datenformate für den zuverlässigen Austausch von Informationen zwischen dem CAD-System und der CAM des Leiterplattenherstellers. Toleranzen in der Auflösung der Datenbasis und die resultierende Konsequenz für diverse technische Eigenschaften der Leiterplatte.

|

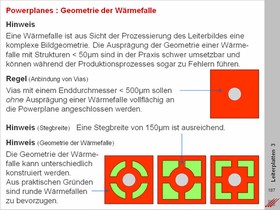

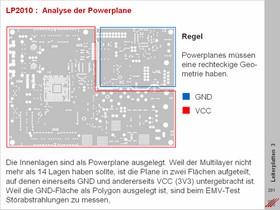

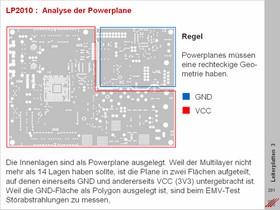

Konstruktion von Powerplanes

Berechnung des minimalen Abstandes zwischen Isolationspads und Powerplanes sowie zu anderen Leiterbildstrukturen.

Definition der Wärmefalle.

Ursachen und Folgen von Schlitzen in Powerplanes. Verbesserung der Signalintegrität.

|

|

|

Elementare Designregeln

Regeln für das Routen von Leiterbahnen und für die Anlage von Padstacks in der CAD-Bibliothek.

Einzuhaltende Abstände zwischen benachbarten Tracks und Pads.

Berücksichtigung von produktionsbezogenen Einflüssen auf das CAD-Design.

|

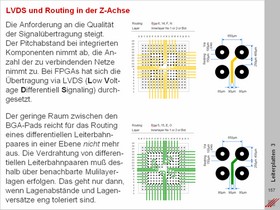

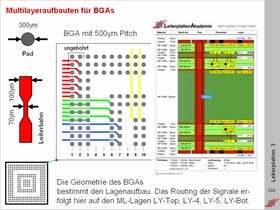

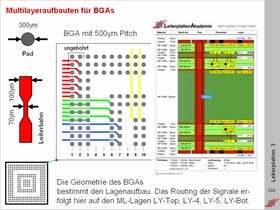

BGA-Routing

Beachtung der Bauteilgeometrien bei den Routingvorgaben. Analyse der erforderlichen Routingkanäle.

Vorgaben für die minimalen Leiterbahnbreiten und die notwendigen Sicherheitsabstände.

Differentielle Impedanzen in der Z-Achsen-Richtung eines Multilayers.

|

|

|

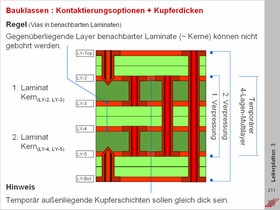

Konstruktion von Multilayern

Regeln für die Konstruktion von Multilayersystemen. Beachtung der materialbezogenen Kupferdicken.

Erforderliche Verpressungen für einen Multilayer auf Grund der Verteilung der Kerne und der Strategie für das Kontaktieren der Lagen.

|

Powerplanes

Konstruktion von Powerplanes für ein Höchstmaß an Signal- und Powerintegrität (siehe ..."LP2010").

Aufteilung von Stromversorgungsflächen mit unterschiedlichen

Potentialen. Randisolationen.

Der Einfluß des Aspect Ratio auf die Geometrien einer Innenlage.

|

|

|

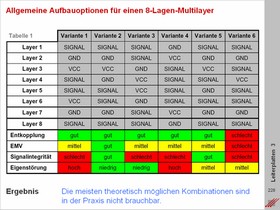

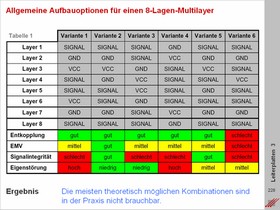

Aufbauoptionen für Multilayer

Strategien für die Konstruktion von Multilayersystemen für High-Speed-Leiterplatten.

Zuordnung idealer Eigenschaften mit Blick auf die Kombination der Lagenfunktionen zueinander.

Schemata für die qualitative Bewertung einer Multilayerkonstruktion.

|

Lagenaufbaustrategien

Lagenaufbauten auf der Basis von Bauteilanschlußvorgaben.

Optimierte Lösungen für preiswerte aber leistungsfähige Multilayeraufbauten für High-Speed-Baugruppen. Konstruktionsvorgaben für das Fan-Out von BGAs. Zuordnung der funktionalen Qualitäten.

|

|

|

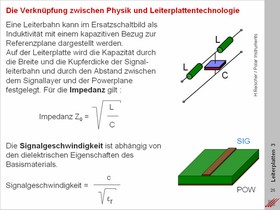

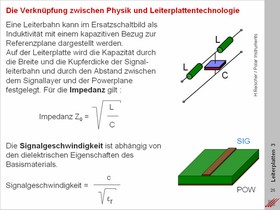

Signalübertragung

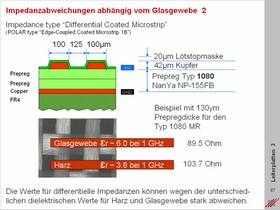

Physikalische Eigenschaften von Signalübertragungsleitungen. Einfache elektrische Eigenschaften von Leiterbildern. Definition von Impedanzmoduln inklusive der Integration in einen Multilayer. Kapazitive Einflüsse auf die Signallaufzeit.

|

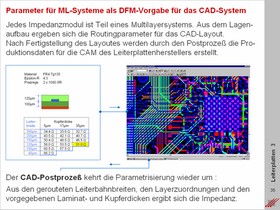

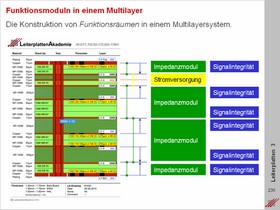

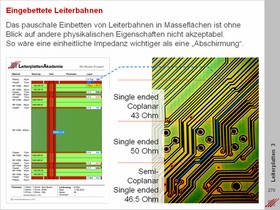

Impedanzmoduln

Nomenklatur für diverse impedanzdefinierte Strukturen. Single-Ended und Differentielle Impedanzen. Allgemeine Standardmoduln. Beispiele für die Berechnung von Impedanzen. Integration der Constraints in das CAD-System als Vorgaben für das Routing.

|

|

|

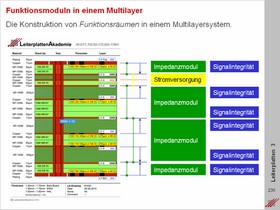

Multilayersysteme

Integration unterschiedlicher Anforderungen in ein Multilayersystem. Berücksichtigung von EMV und Signalintegrität.

Multipowersysteme mit Referenzplanes zur Vermeidung von Übersprechen. Beachten der Signal- und der Stromversorgungsräume.

|

Was leistet das Seminar " Leiterplatten 3 …HighSpeedLeiterplatten und für wen ist es zu empfehlen?

Alles wird schneller. Steigende Taktraten und hohe Datentransferraten bestimmen den elektronischen Alltag. Vor allem aber nehmen die Signalanstiegszeiten der modernen Bauteile drastisch ab.

Weil sich mit der Übertragungsgeschwindigkeit auch die qualitativen Anforderungen an die physikalische Funktion der Baugruppe ändern, hat diese Entwicklung einen massiven Einfluß.

Die Signalintegrität, EMV und Powerintegrität sind besonders zu beachten. Das CAD-Layout und die Leiterplatte (…üblicherweise ein Multilayer) müssen die technischen Anforderungen umsetzen.

Weil das CAD-Layout die geometrischen Forderungen an die Leiterplatte definiert, gilt es, den Einfluß von Leiterbahnbreiten und Lagenaufbauten genau zu kennen.

Die Eigenschaften der eingesetzten Laminate und Substrate sind wichtig. Die Prozessierung der Drucke und die Durchführung diverser galvanotechnischer Arbeitsgänge haben eine Auswirkung auf die Signallaufzeit und auf die Signalübertragungsqualität.

Die Konstrukteure elektronischer Baugruppen müssen die physikalischen Auswirkungen diverser mechanischer und geometrischer Varianten bei der Konzeption eines Gerätes berücksichtigen. Nur dann ist ein zuverlässiger und langfristig störungsfreier Betrieb gewährleistet.

Insbesondere gilt es, den Einfluß der wichtigsten Produktionsschritte für eine Leiterplatte richtig einschätzen zu lernen und gezielt für eine sicher vorhersagbare Baugruppenfunktion zu nutzen.

Das Seminar richtet sich an Baugruppenkonstrukteure, Schaltungsentwickler und CAD-Designer/innen. Es ist auch sinnvoll für die CAM-Bearbeiter/innen der LP-Hersteller, weil es die verschachtelten Zusammenhänge zwischen CAD und Leiterplatte erläutert. Es fördert somit das partnerschaftliche Miteinander auf der Linie "CAD - CAM - Leiterplatte".

Die übersichtliche und strukturierte Darstellung der Themen ist ebenfalls interessant für alle, deren Aufgabe es ist, das Produkt "Baugruppe" führend und beratend zu begleiten.

Ihr Referent

|

Arnold Wiemers ist der Leiterplatte seit 1983 verbunden. Von 1985 bis 2009 war er bei der ILFA GmbH in Hannover beschäftigt.

Er war dort verantwortlich für die Fachbereiche CAD und CAM, für die Auftragsvorbereitung und für die technische Dokumentation der Firma ILFA im Internet.

Er arbeitet seit 1982 als freier Softwareentwickler, vornehmlich für branchentypische Applikationen im Bereich der Leiterplatte, wie die Kalkulation und die Fertigungssteuerung von Leiterplatten.

|

Seit 2009 ist er Teilhaber und Technischer Direktor der LeiterplattenAkademie.

Diverse Fachveröffentlichungen. Referent für Seminare, Konferenzvorträge und Workshops zum Thema Leiterplattentechnologie (MFT, MPS, Impedanz, Multilayersysteme, Gerber, Designregeln, LP2010).

Vom IPC zertifizierter CID, CID+ und Instructor. FED-Designer und FED-Referent. Mitarbeit am Schulungskonzept des FED. Mitarbeit in der internationalen "Projektgruppe Design" des FED und des VdL.

Teilnahmegebühren

PräsenzSeminar: Die Teilnahmegebühr beträgt € 520,- pro Person zzgl. MwSt. Enthalten sind ein Mittagessen sowie Pausengetränke. Jeder Teilnehmer erhält ausführliche Seminarunterlagen und ein Zertifikat.

OnlineSeminar: Die Teilnahmegebühr beträgt € 480,- pro Person zzgl. MwSt. Jeder Teilnehmer erhält ausführliche Seminarunterlagen und ein Zertifikat.

Seminare im Rahmen einer mehrtägigen Veranstaltungsreihe können im Paket gebucht werden. Bei Buchung mehrerer Seminare erhalten Sie eine Ermäßigung von 75,00 Euro pro Seminar.

Da unsere Online-Anmeldeforlulare jeweils für die Buchung einzelner Seminare ausgelegt sind, empfiehlt sich für eine evtl. Paket-Buchung mehrerer Veranstaltungen eine formlose Anmeldung unter anmeldung@leiterplattenakademie.de

Anmeldebedingungen

Aus organisatorischen Gründen ist die Teilnehmerzahl begrenzt. Anmeldungen werden in der Reihenfolge des Eingangs berücksichtigt. Bitte zahlen Sie erst nach Erhalt der Rechnung. Der Veranstalter behält sich das Recht vor, das Seminar auch nach erfolgter Anmeldebestätigung unter Rückerstattung der Gebühren abzusagen. Nähere Informationen zur Anreise erhalten Sie mit der Rechnung/Anmeldebestätigung.

Eine schriftliche Stornierung der Anmeldung ist bis eine Woche vor dem Veranstaltungstermin gegen eine Bearbeitungsgebühr in Höhe von 40,00 € möglich, danach ist in jedem Falle der gesamte Betrag fällig. Der Teilnehmer kann den Seminarbesuch jedoch innerhalb eines halben Jahres nach dem Seminartermin nachholen.

|