# LeiterplattenAkademie

*Gerhard Eigelsreiter* *Unit^el*

## Seminar

# LP2010 R3

**Design und Realisierung

von High-Speed-Hardware**

**Das Seminar zur erfolgreichen Serie

"Die Leiterplatte 2010"**

## Was leistet das "LP2010"- Seminar und wer wird angesprochen?

Die Entwicklung bei den aktiven elektronischen Bauteilkomponenten führt zu hoch getakteten CPUs und zu Signalflanken, die im Bruchteil einer Nanosekunde ansteigen.

Die Aufgabe vieler künftiger Applikationen wird die ultraschnelle Verarbeitung von Datenmengen im Gigabit-Bereich sein.

Das "LP2010"-Seminar erläutert die notwendigen Voraussetzungen für einen erfolgreichen Lösungsweg. Angesprochen werden **Schaltungsentwickler/innen** und **CAD-Designer/innen**.

Vor dem Hintergrund der geänderten physikalischen Rahmenbedingungen werden konkrete Strategien für die Konzeptionierung von Hochgeschwindigkeitsplattformen für die Gigabit-Technik vorgestellt.

Schwerpunkte sind die systematische Auswahl der Bauelemente, das Leiterplattenlayout, die Eigenschaften impedanzdefinierter Leiterbahnen, die äußere und innere EMV, die Integrität von Signalen und Stromversorgungssystemen sowie erprobte Multilayer-Aufbauten für diese Aufgabenstellungen.

Die Beispiele im Seminar basieren auf Baugruppen der Firma unit^el, die sich in der täglichen Anwendung bewiesen haben.

Von der Fachzeitschrift **ElektronikPraxis** wurde die CPU "CERO" für die Veröffentlichung als "Leiterplatte 2005" ausgewählt, und die CPU "meltemi" als "Leiterplatte 2010".

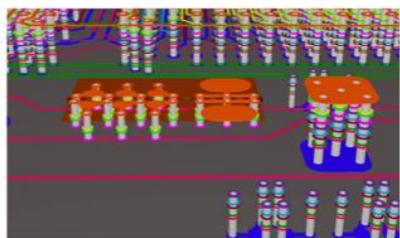

## meltemi Board (20 Lagen Original)

Funktion / Blockschaltbild

© unitel IT-Innovationen | Alle Rechte vorbehalten | [www.unitel.at](http://www.unitel.at) | [info@unitel.at](mailto:info@unitel.at) | Seite 1

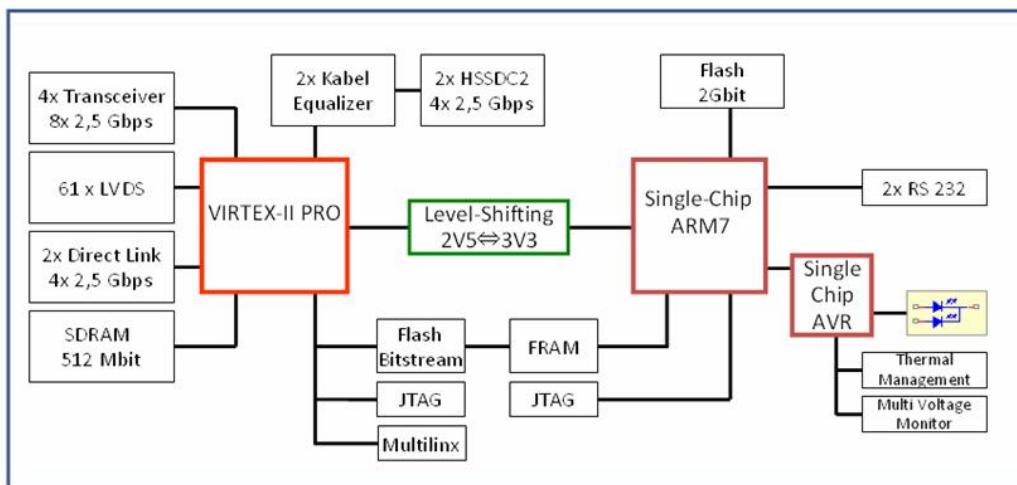

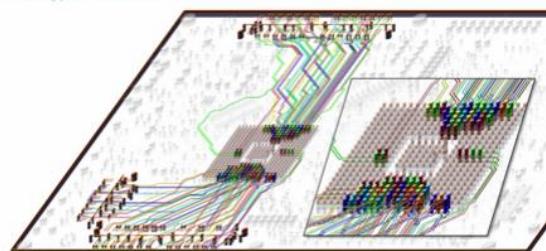

## meltemi - LP2010 / Blockschaltbild

Aufbaukonzept für ein MCC (Multifunktional Circuit Carrier System) auf der Basis eines Virtex-Transceivers mit peripheren Funktionsblöcken.

Transfer via LVDS-Leitungen. Single-Chip ARM7. Speichergruppen, Schnittstellen und Übertragungseigenschaften im GBit-Bereich.

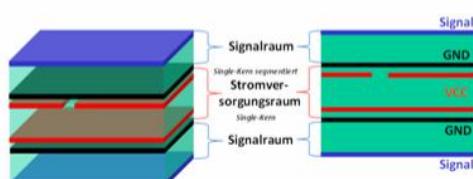

### Lagenaufbau

Durch das gezielte Anordnen der Lagen werden Funktionsräume gebildet

## Multilayer-Architektur

Konzepte für die breitbandige Verarbeitung von Signalen. Aspekte der Konstruktion und des Leistungspotentials von MCCs. Sorgfältige Aufteilung der Funktionen eines Multilayers in Stromversorgungsräume und in Signallräume. Aufbauvorschläge.

## Verwendete Logik-Familien

Passiv

### AUP

Ausgelegt für Betriebsspannungen von 0.8V bis 3.6V

3.6V I/O Toleranz

Eingangs-Hysterese – 250mV typisch bei 3.3V

Extrem niedriger Stromverbrauch

### CB3T

3.3/2.5V Bus-Schalter mit 5 V tolerantem Pegelwandler

5V Eingang mit Pegelwandlung auf 3.3V bei 3.3VCC

5V und 3.3V Eingang mit Pegelwandlung auf 2.5V bei 2.5VCC

Sehr gut für Batteriebetrieb geeignet (Betriebsstrom einige  $\mu$ A)

© unitel IT-Innovationen | Alle Rechte vorbehalten | [www.unitel.at](http://www.unitel.at) | [info@unitel.at](mailto:info@unitel.at) | Seite 3

## Bauteilauswahl 1

Spezifikation von Bauteilen. Argumente für erforderliche Einsatzbereiche. Einfluß und Folgen reduzierter Betriebsspannungen. Reduzierung der Flankensteilheit. Auswahl von Logikfamilien und Busschaltern. Aktive Terminierung von Signalleitungen. Reprogrammierbare Logik. Einflußnahme auf die Flankensteilheit per Software. Einsatz und Möglichkeiten von FPGAs.

### Glue-Logik und Mikroprozessor

Logikfamilienwahl – meltemi

Aktive / Passive Komponenten

CPU <> MPU - meltemi

Spannungsregelung

Stromversorgungsentkopplung

## Bauteilauswahl 2

Auswahl der aktiven und passiven Komponenten. Die Abstimmung zwischen der CPU und der MPU auf dem meltemi-Board. Vorgaben für die Bauteile zur Entkopplung der Stromversorgung. Die Interpretation von Leistungsangaben in Datenblättern.

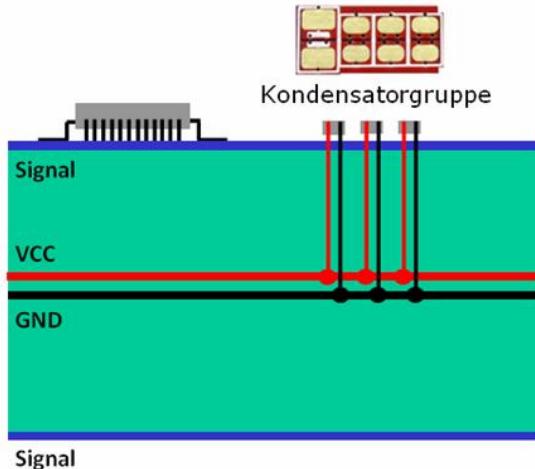

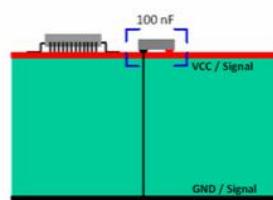

## Stromversorgungssystem

4 Lagen-Multilayer (50µm)

Aus Sicht der EMV: Brauchbar

Stützung: Ausreichend

Absorption: Gegeben

Erklärung:

Dünne Lamine zwischen VCC und GND erhöhen die Flächenkapazität massiv. Absorption durch ausreichend kleinen Wellenwiderstand des VCC – GND Flächensystems  $< 1$  Ohm. Geforderte Breitbandigkeit nur in Kombination mit einer berechneten Kondensatorgruppe erzielbar.

© unitel IT-Innovationen | Alle Rechte vorbehalten | www.unitel.at | info@unitel.at | Seite 5

## Stromversorgung 1

Stromversorgungssysteme für Baugruppen. Strategien für die Stromversorgung durch den Aufbau von Multilayern.

Vorteile in der Layoutgestaltung durch das Pluggen von Vias.

Abschirmung von Leiterplattenbereichen durch die Metallisierung der Leiterplattenkanten ("Kantenkontaktierung").

### Stromversorgungssystem

2 Lagen-Board

Aus Sicht der EMV: Unbrauchbar

Stützung: Keine

Absorption: Keine

Erklärung:

In Folge zu hoher parasitärer Induktivitäten kann die schnellen Halbleiter-ICs benötigte Ladung nicht zeitgerecht bereit gestellt werden.

## Stromversorgung 2

Mängel in der Stromversorgung einfacher 2-Lagen-Boards.

Der Einfluß parasitärer Induktivitäten auf die Stabilität der Schaltungsfunktion.

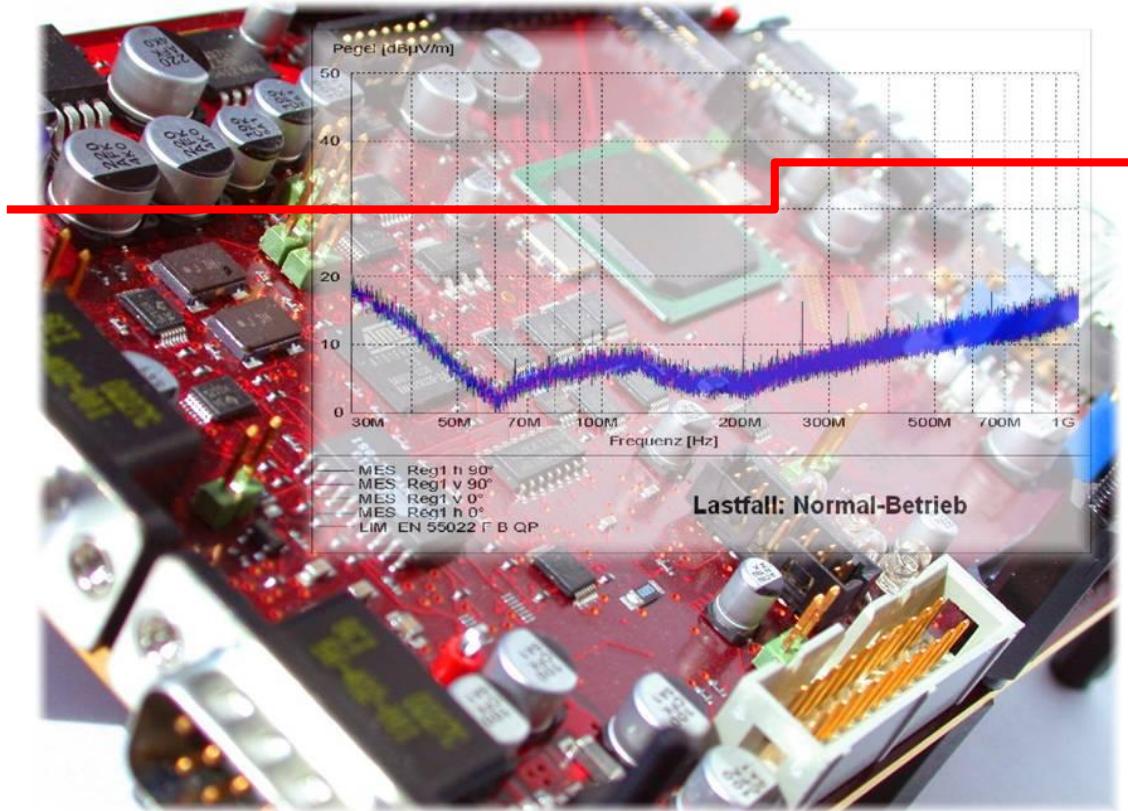

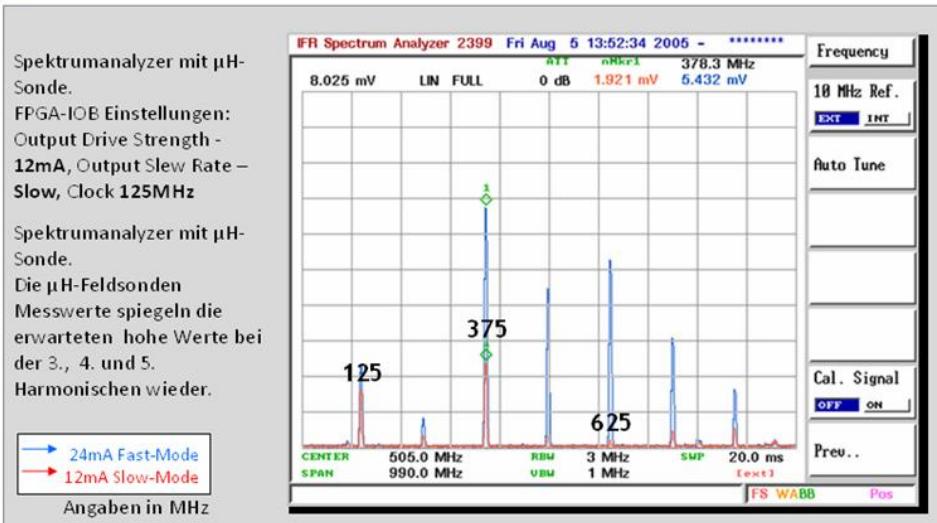

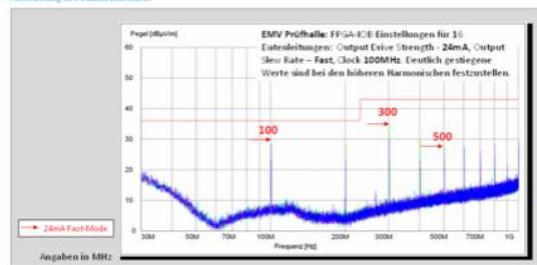

## FPGA-D26 125MHz 12mA Slow & 24mA Fast

Spektrum - melemi

© unitel IT-Innovationen | Alle Rechte vorbehalten | www.unitel.at | info@unitel.at | Seite 7

## Funktionsanalyse

Technische Aspekte bei der Messung des Abstrahlverhaltens von High-Speed-Baugruppen.

Die Betrachtung und die Auswertung diskreter Frequenzen.

Gegenüberstellung von Taktrate und Bandbreite mit Blick auf die Hochgeschwindigkeitseigenschaften einer Baugruppe.

Diskussion kritischer Frequenzbereiche.

### EMV Prüfhalle

Änderung der Flankensteilheit

## EMV-Messung

Allgemeine Vorgaben für die Durchführung von Messungen im EMV-Labor.

Interpretation von Meßergebnissen in den unterschiedlichen Frequenzbereichen.

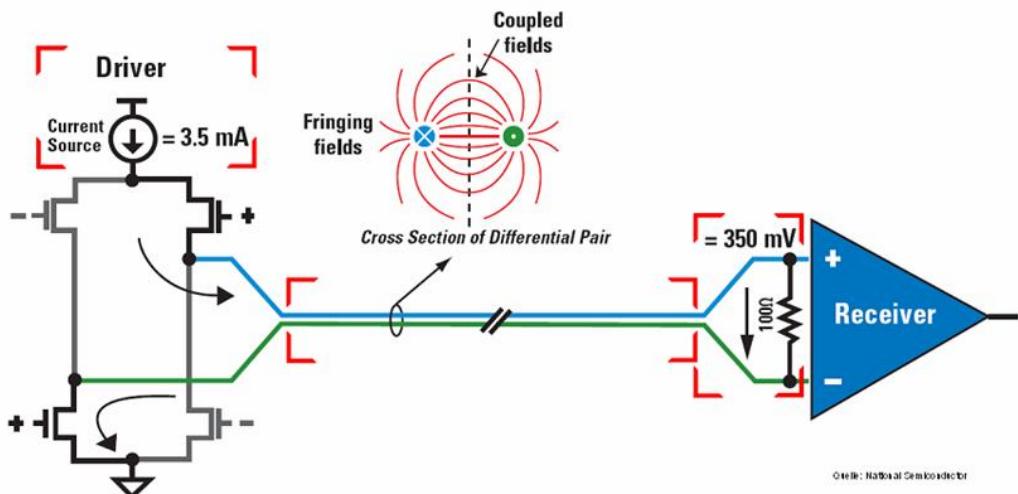

## LVDS

© unitel IT-Innovationen | Alle Rechte vorbehalten | [www.unitel.at](http://www.unitel.at) | [info@unitel.at](mailto:info@unitel.at) | Seite 9

## Diskussion der technischen Vorgaben an das CAD-Layout

Allgemeine Signalintegrität. Beachtung der internen Gatterlaufzeiten und der Signalübertragungseigenschaften von Leiterbahnen.

Berechnung und Durchführung des Längenausgleich bei differentiellen Signalen. LVDS-Verbindungen. Berücksichtigung der Impedanz von Signalleitungen. Anforderungen an die USB-Schnittstelle.

Vorschläge für das Routing der Leiterbahnen am CAD-System.

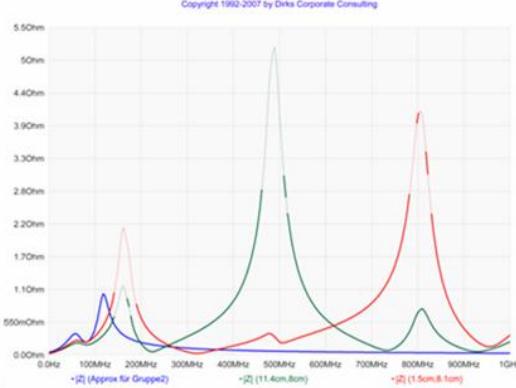

### Kondensatorgruppe

Layout - Beispiel einer Kondensatorgruppe mit 4 X7R-MLC-Kondensatoren; Layoutform  $\rightarrow$  1x1200, 2x480

© unitel IT-Innovationen | Alle Rechte vorbehalten | [www.unitel.at](http://www.unitel.at) | [info@unitel.at](mailto:info@unitel.at) | Seite 10

## Breitbandentkopplung

Strategien für die Entkopplung der unterschiedlichen Stromversorgungen einer Baugruppe über gerechnete Kondensatorgruppen. Layoutvorgaben für die Plazierung und die Anbindung der Kondensatoren über Vias an die Stromversorgungsflächen.

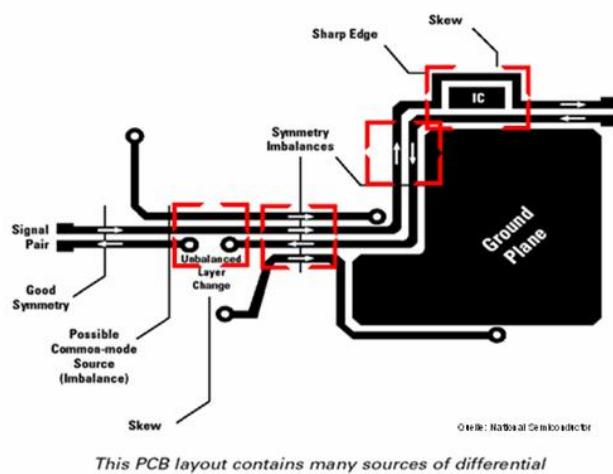

## LVDS Layout-Richtlinien

Ein „Gruppenfoto“ der häufigsten Fehler in der differentiellen Leistungsführung

## Layout-Regeln zur Beachtung der Signalintegrität

Vermeidung unsymmetrischer Leiterbahnführung. Beachtung und Definition der GND-Bezüge für die Rücklaufströme in einer High-Speed-Umgebung. Maßnahmen für die Reduzierung der EMV-Emission.

Aufbaustrategien für 6-, 8-, und 10-Lagen-Multilayer mit Blick auf die Realisierung einer hohen Signalintegrität.

### LVDS – Routing

© LVDS Leitungsspace - mehrmals 85/12F-MCC

## LVDS-Routing

Vorgaben für LVDS-Signalleitungen. Einbindung der Signallayer in das MCC-Konzept. Strategien für das Entflechten von integrierten FPGA-Bausteinen. "Single-Ended"-Impedanzen und differentielle Impedanzen.

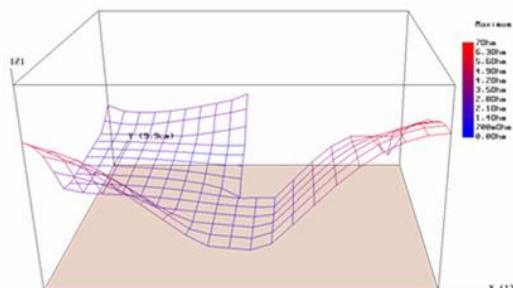

## Segmentierung der Stromversorgungsflächen

Lageaufbau; Fläche 9,9cm x 13,9cm mit Segmentierung 4,9cm x 6,9cm

**Kondensatorgruppenberechnung:**

Problemstellung: Segment A bildet ein **nicht** erlaubtes Polygon (Sonderfall eines Schlitzes)

© unitel IT-Innovationen | Alle Rechte vorbehalten | [www.unitel.at](http://www.unitel.at) | [info@unitel.at](mailto:info@unitel.at) | Seite 13

## Eigenschaften von Stromversorgungsflächen

Simulation, Berechnung und Geometrie niederimpedanter Stromversorgungssysteme. Stützung und Absorption. Nutzung der kapazitiven Eigenschaften von flächig ausgelegten Powerplanes.

Berücksichtigung des Wellenwiderstandes des VCC-GND-Systems. Ergänzung der Entkopplungseigenschaften durch eine gerechnete Kondensatorgruppe.

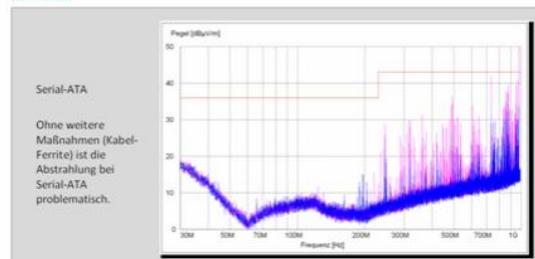

### Vergleich – Infiniband & Serial-ATA

EMV-Freifläche

Serial-ATA

Ohne weitere Maßnahmen (Kabel-Ferrite) ist die Abstrahlung bei Serial-ATA problematisch.

## Übertragungskabel

Vergleich von Infiniband und SATA-Kabel. Abstrahlverhalten bei der Nutzdatenübertragung im GByte-Bereich. Betrachtung kritischer Frequenzbänder. Ursachen für Diskontinuitäten bei der Signalqualität.

## Ihr Referent

**Gerhard Eigelsreiter**, Inhaber von unit^el, (Graz) entwirft seit 1972 Mikroprozessor System-Hardware auf Board Ebene. Ausgerichtet auf die harten industriellen Anforderungen entwickelte er bereits 1981 die universelle Applikationsplattform Versacom-I. Weitere SBC-Designs mit Schwerpunkt FPGAs folgten. Ausgedehnte Grundlagenforschungen kombiniert mit den Erfahrungen aus zwanzigjähriger Praxis im Umgang mit

FPGAs bildeten die Basis für die Entwicklung von Hochgeschwindigkeits-Embedded-Hardware mit ausgeprägten EMV-Eigenschaften und charakteristischer, hoher funktionaler Stabilität.

Veröffentlichungen: Fachartikel in den Zeitschriften Design&Elektronik und Elektronik Praxis mit den Artikelserien "**Die Leiterplatte 2005**" und "**Die Leiterplatte 2010**", sowie das zweisprachige Sonderheft "Die Leiterplatte 2005".

## Die LeiterplattenAkademie

Die Sicherung des Standortes Deutschland in Europa und der Erhalt der internationalen Wettbewerbsfähigkeit setzt eine systematische und kontinuierliche Qualifikation der Mitarbeiter/innen eines Unternehmens voraus.

Die wirtschaftliche Leistungsfähigkeit einer Industriegesellschaft und ihre technologische Kompetenz am Weltmarkt wird (auch) durch die Qualität ihrer Elektronikprodukte bestimmt.

Das bedeutet eine fachlich hochwertige Aus- und Weiterbildung.

Die zentrale Aufgabe der LeiterplattenAkademie ist, das Fachwissen aus den Bereichen der Schaltungsentwicklung, des CAD-Designs, der CAM-Bearbeitung, der Leiterplattentechnologie und der Baugruppenproduktion in Seminaren, Workshops und Tutorials zu vermitteln.

## **Seminare und Teilnahmegebühren**

Das Tagesseminar "Ip2010" wird als freies Seminar durchgeführt, kann für Konferenzen gebucht werden und steht auch als InHouse-Seminar zur Verfügung.

### ***Freies Seminar***

Die Durchführung liegt bei der LeiterplattenAkademie. Die Termine werden via Mailing, eMail, Internet oder Presseveröffentlichungen mitgeteilt. Die Veranstaltungsorte sind in Deutschland, Österreich und der Schweiz. Die Teilnahmegebühr beträgt 520 € zzgl. MwSt. pro Person. Inklusive ausführlicher Seminarunterlagen, Teilnahmezertifikat, Essen und Getränke.

### ***Konferenz-Seminar***

Wenn Sie "Ip2010" auf Ihrer Konferenz anbieten möchten, dann sprechen Sie bitte unsere Seminarleitung an.

### ***InHouse: Unser Seminar in Ihrem Haus***

"Ip2010" wird auch firmenintern referiert. Sie sparen sowohl Reise- als auch Übernachtungskosten, vor allem jedoch Zeit.

Ab 2.000 € zzgl. MwSt. für 4 Teilnehmer liefern wir Ihnen unseren Referenten "frei Haus". Für jeden weiteren Teilnehmer bis 10 Personen berechnen wir Ihnen 150 € p.P. Weitere Teilnehmer auf Anfrage.

Eine individuelle Themengestaltung mit firmentypischen Schwerpunkten ist selbstverständlich möglich. Bitte stimmen Sie sich mit uns ab: [inhouse@leiterplattenakademie.de](mailto:inhouse@leiterplattenakademie.de)

Jeder Teilnehmer erhält ausführliche Seminarunterlagen sowie ein Teilnahmezertifikat.

Wir bieten Ihnen 15% Rabatt für InHouse-Seminare in den Monaten Juli und August.

# LeiterplattenAkademie

## *Die LeiterplattenAkademie*

Die LA - LeiterplattenAkademie GmbH ist eine Schulungs- und Weiterbildungseinrichtung für die Fachbereiche

**Schaltungsentwicklung**

**CAD-Design**

**CAM-Bearbeitung**

**Leiterplattentechnologie**

**Baugruppenproduktion**

Die Akademie versteht sich als Partner für öffentliche Einrichtungen und Unternehmen der Wirtschaft, die in vergleichbaren Feldern engagiert sind.

**LA - LeiterplattenAkademie GmbH**

**Krefelder Straße 18**

**10555 Berlin**

Telefon (030) 34 35 18 99

Telefax (030) 34 35 19 02

eMail [info@leiterplattenakademie.de](mailto:info@leiterplattenakademie.de)